# HI EFFICIENT

WIDE-BANDGAP TECHNOLOGIES FOR TOMORROW'S HIGHLY EFFICIENT AND RELIABLE AUTOMOTIVE MOBILITY SOLUTIONS

### "A new frontier in GaN power technology: GaN System-on-Chips for power electronic applications"

#### Herbert De Pauw (imec)

This project has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No. 101007281. The JU receives support from the European Union's Horizon 2020 research and innovation programme and Austria, Germany, Slovenia, Netherlands, Belgium, Slovakia, France, Italy, and Turkey.

### Outline

- Introduction

- GaN base line technology 100V and 650V

- GaN System-on-Chip features

- GaN power HEMTs in HB configuration

- Integrated gate driver with/without levelshifters

- PWM generator

- 4-terminal or 2-terminal temperature sensors

- 1% current-sense terminals

- GaN System-on-Chip realisations and measurements

#### 24 September 2024

### and digital technologies

• IMEC

- headquarters in Leuven (Belgium) •

- > 12000m<sup>2</sup> cleanroom capacity

- > 5,500 skilled people over 95 nationalities

- driving advances in microchip technology

#### $\Rightarrow$ www.imec.be

Introduction

### GaN at IMEC

- 20 engineers + operators

- 3 dedicated teams

- Epitaxy

- Integration

- Device

- 15+ years of experience

- 200mm fab

- Transition to 300mm fab

- 3000 GaN-wafers grown per year

### • Why GaN ?

- bench marks for power switches

- On-state  $\Rightarrow$  resistance as low as possible

- Off-state  $\Rightarrow$  block high-voltage with low leakage current

- trade-off between on-state and off-state

$$R_{ON} = \frac{4 \cdot V_{BD}^2}{\epsilon_{S} \cdot \mu_n \cdot E_c^3}$$

B. J. Baliga, 'Fundamentals of power semiconductor devices,' Springer, 2008.

|         | ε <sub>s</sub> . μ <sub>n</sub> . Ε <sup>3</sup> |

|---------|--------------------------------------------------|

| Si      | 1                                                |

| 4H-SiC  | 207                                              |

| h-GaN   | 1191                                             |

| Diamond | 4267                                             |

- Why GaN System-on-Chip (GaN SoC) ?

- size reduction

- single chip solution vs multiple chip solutions

- exploit the GaN power HEMT to its maximum

- by monolithic integration of the gate driver

- reduced parasitics (R,L and C)

- increased switching frequency

- smaller passives

- by introducing extra functionality

- over- and under-voltage protection

- gate signal generation

- dead-time control

- ...

GaN SoC applications in Hi EFFICIENT

#### powertrain inverters

### vehicle solar panel converter

### on-board charger

### Outline

- Introduction

- GaN base line technology 100V and 650V

- GaN System-on-Chip features

- GaN power HEMTs in HB configuration

- Integrated gate driver with/without levelshifters

- PWM generator

- 4-terminal or 2-terminal temperature sensors

- 1% current-sense terminals

- GaN System-on-Chip realisations and measurements

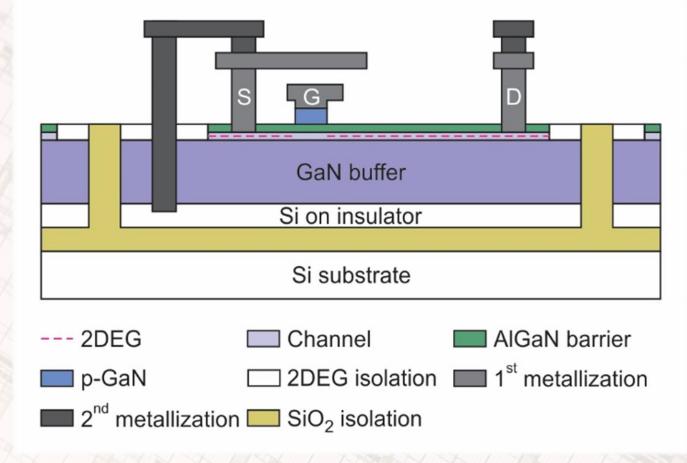

### GaN base line technology for 100V and 650V

### GaN base line technology for 100V and 650V

- Available devices

- HV power HEMT

- Vthreshold = 2.5V

- LV HEMT

- Vthreshold = 2.5V

- high-ohmic / low-ohmic resistor

- capacitors

⇒ resistor-transistor logic circuits / analog circuits

### Outline

- Introduction

- GaN base line technology 100V and 650V

- GaN System-on-Chip features

- GaN power HEMTs in HB configuration

- Integrated gate driver with/without levelshifters

- PWM generator

- 4-terminal or 2-terminal temperature sensors

- 1% current-sense terminals

- GaN System-on-Chip realisations and measurements

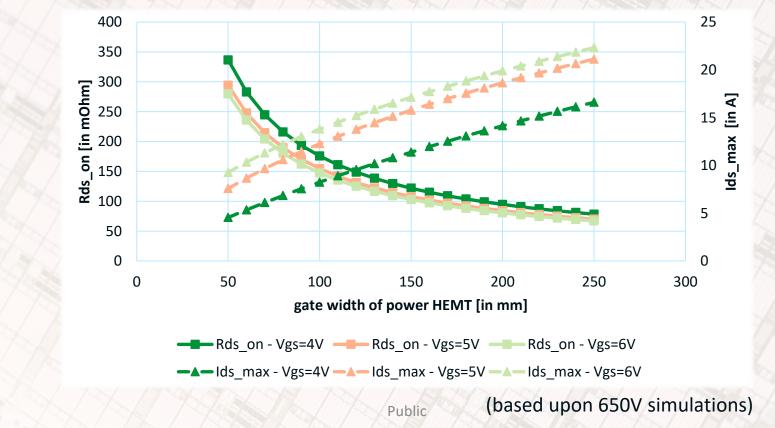

### GaN power HEMT

Rds\_on / Ids\_max versus Vgs variation

### GaN power HEMT

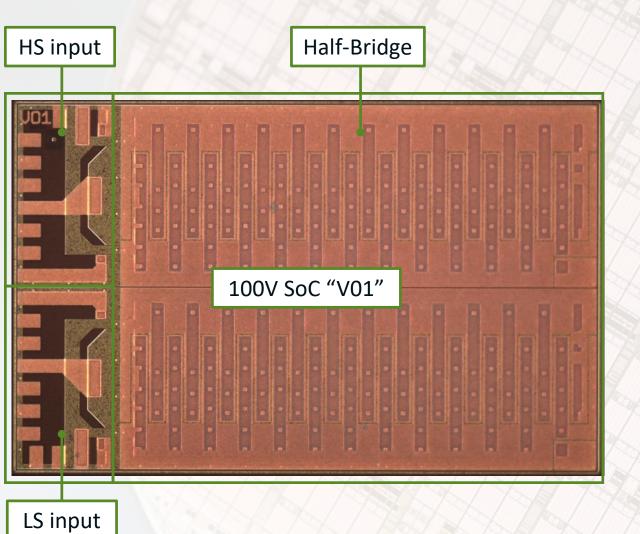

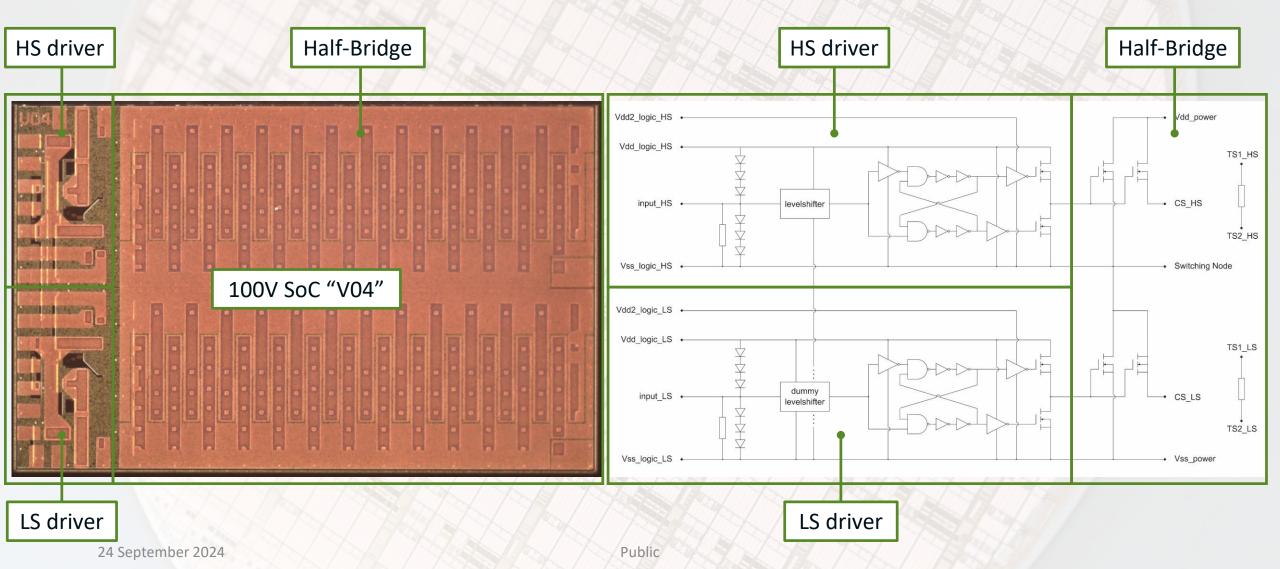

#### 100V SoCs

| Gate width | Rds_on                 | lds_max |

|------------|------------------------|---------|

| 1000mm     | $8.5 \mathrm{m}\Omega$ | 125A    |

| 750mm      | $10 \text{m}\Omega$    | 100A    |

| 500mm      | $15 \text{m}\Omega$    | 70A     |

| 160mm      | $45 \mathrm{m}\Omega$  | 25A     |

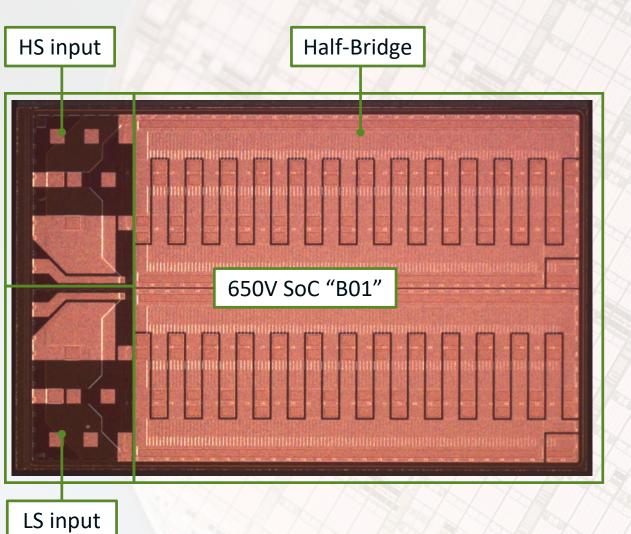

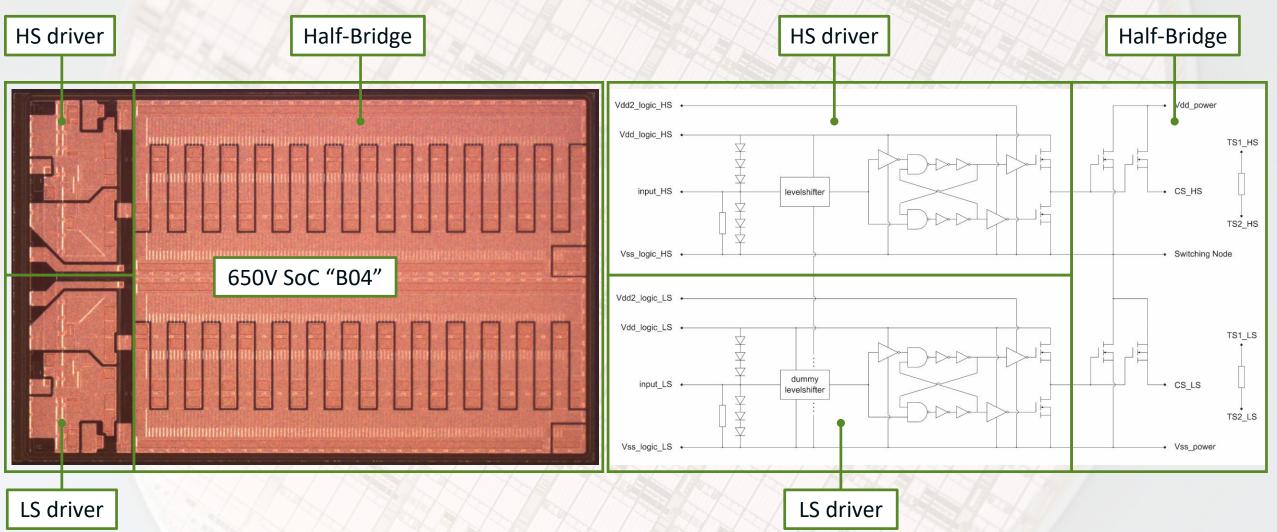

#### 650V SoCs

| Gate width | Rds_on               | lds_max |

|------------|----------------------|---------|

| 157mm      | 105m $\Omega$        | 16A     |

| 140mm      | 115m $\Omega$        | 15A     |

| 125mm      | 130m $\Omega$        | 14A     |

| 117mm      | 135m $\Omega$        | 13A     |

| 50mm       | $300 \text{m}\Omega$ | 7A      |

Rds\_on conditions: Vgs=5V, Vds=1V, temperature=25°C Ids\_max conditions: Vgs=5V, temperature=25°C

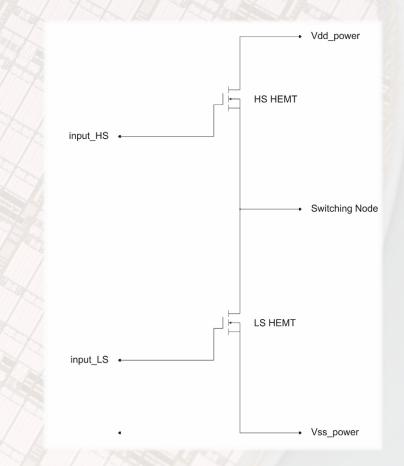

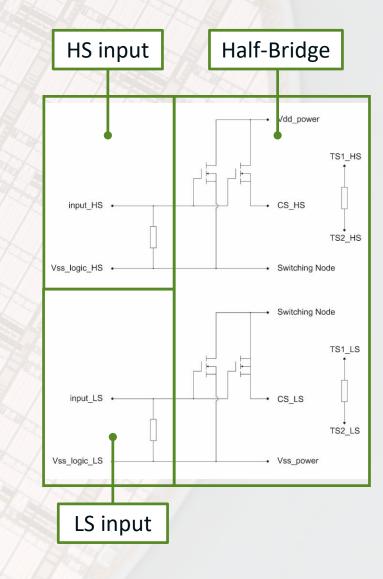

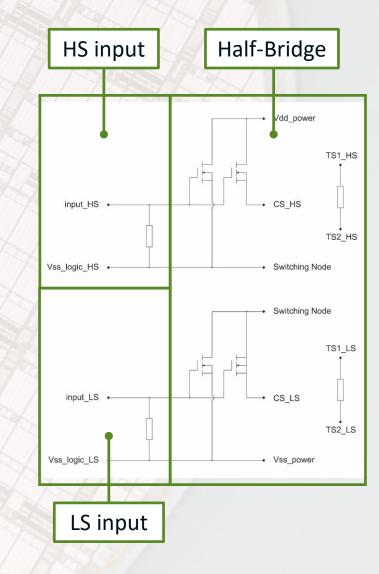

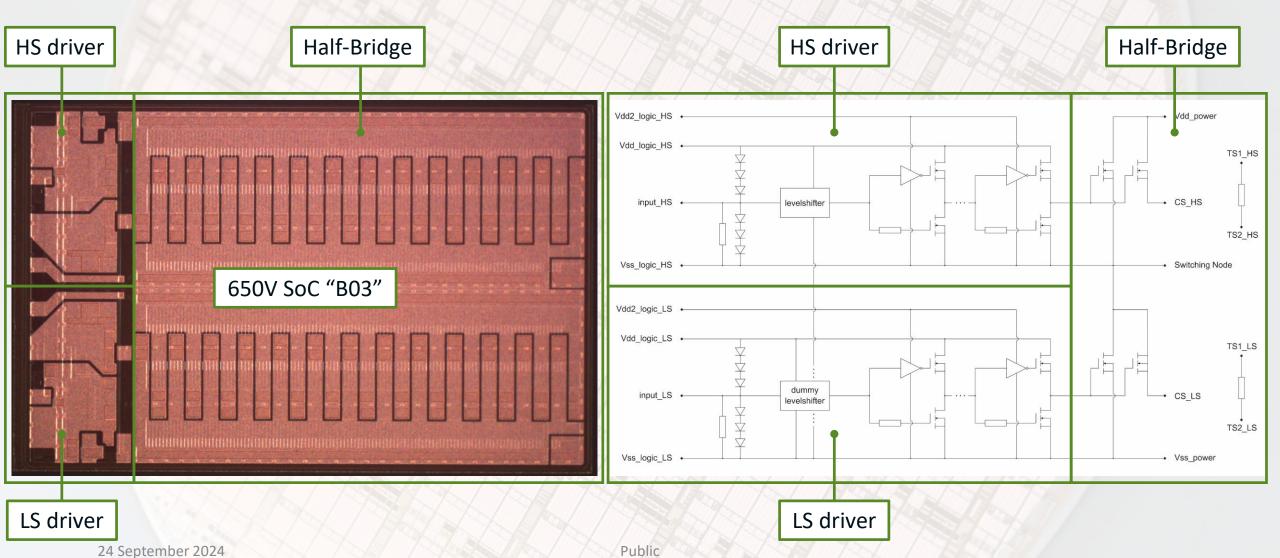

- GaN power HEMTs in HB configuration

- 2 power HEMTs in series

- LS HEMT and HS HEMT

- in separate HV pockets

- 2 LV terminals

- 3 HV terminals

- symmetrical or asymmetrical

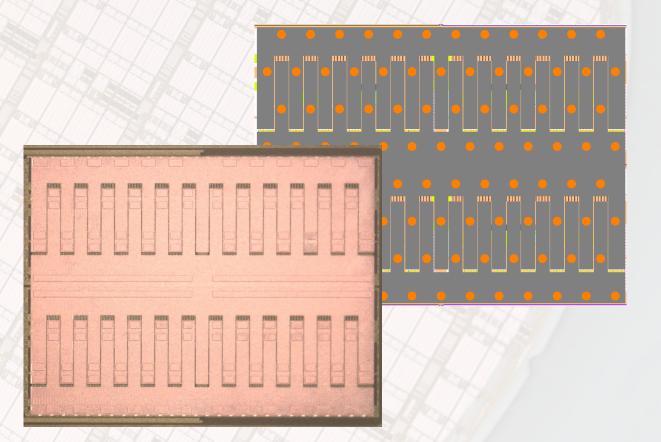

- GaN power HEMTs in Half-Bridge (HB) configuration

- Largest part in SoCs

- 1000mm HB in 100V

- 157mm HB in 650V

#### Layout

- top metal Cu = grey color

- connections = orange circles

- area distributed

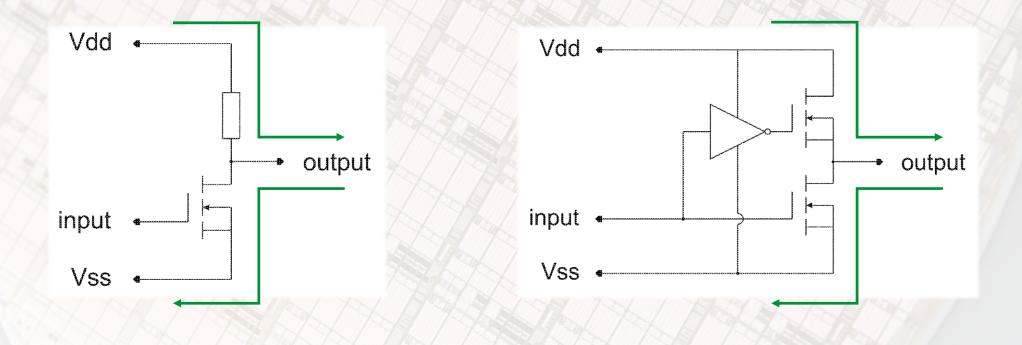

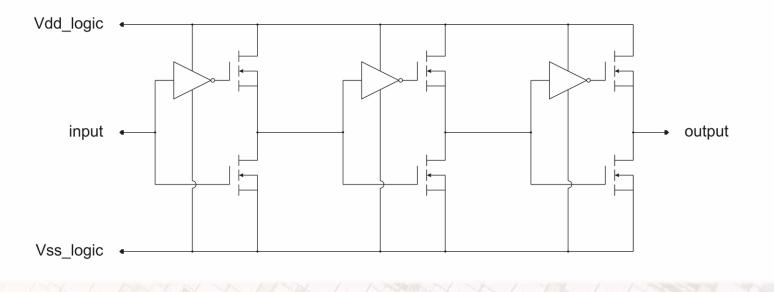

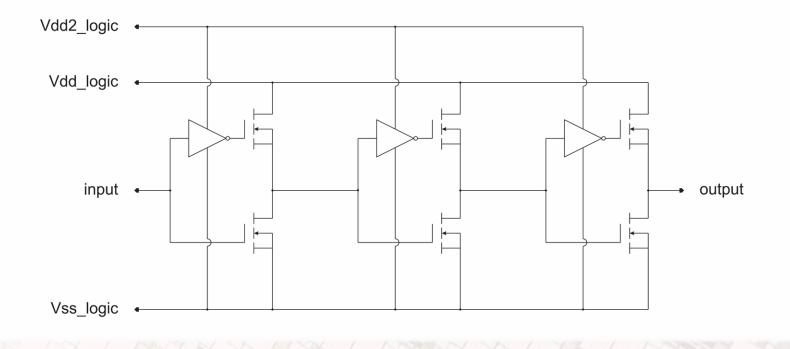

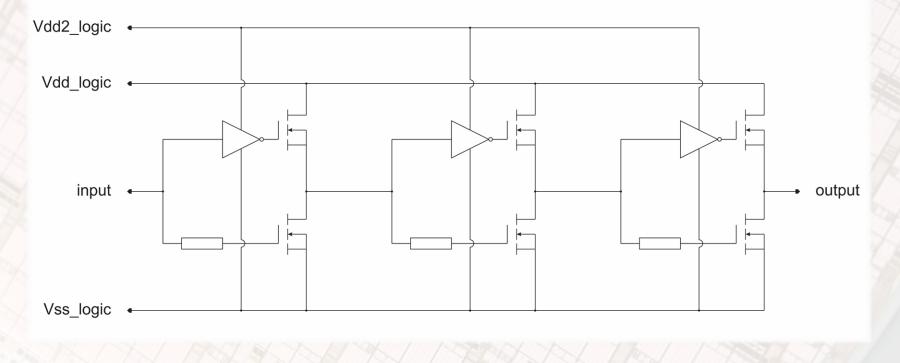

#### Integrated gate driver

• 'inverter' vs 'push-pull' implementation

- Integrated gate driver

- single-supply push-pull version

- Integrated gate driver

- dual-supply push-pull version

- Integrated gate driver

- dual-supply push-pull version with 'delay' resistors

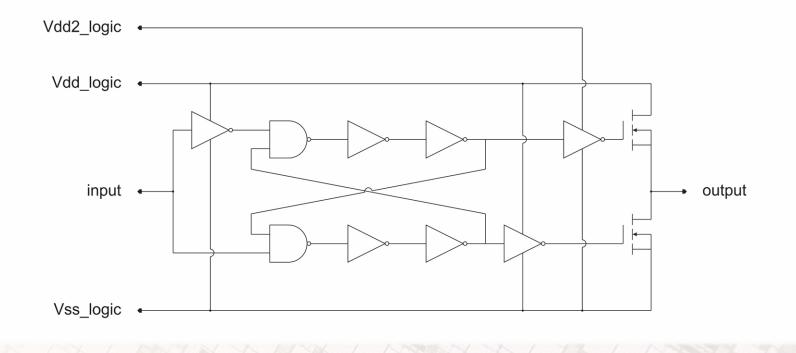

- Integrated gate driver

- cross-coupled NAND port version

| PWM generator     |                                                                                                                                  |                                   |                            |                |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------|----------------|

|                   |                                                                                                                                  |                                   | dead-time control inputs   | dead time      |

| input PWM signal  | 7.7                                                                                                                              |                                   | all DTx='0'                | 24ns           |

|                   | 5                                                                                                                                |                                   | DT1='1', other DTx='0'     | 33ns           |

|                   |                                                                                                                                  |                                   | DT1=DT2='1', other DTx='0' | 42ns           |

|                   | cx:63.714ns                                                                                                                      | DT1=DT2=DT3='1', other<br>DTx='0' | 50ns                       |                |

|                   |                                                                                                                                  | DT1=DT2=DT3=DT4='1',DT4<br>='0'   | 63ns                       |                |

| non-overlapping P | WM signals                                                                                                                       |                                   | All DTx='1'                | 74ns           |

|                   | 5.0 <sup>-1</sup><br>4.0<br>3.0 <sup>-1</sup><br>2.0 <sup>-1</sup><br>1.0 <sup>-1</sup><br>-1.0 <sup>-1</sup><br>4.0 4.2 4.4 4.6 | 4.8 5.0 5.2 5.4<br>time (us)      | 5.6 5.8 6.0 6.2 6.4 (valid | for 1MHz input |

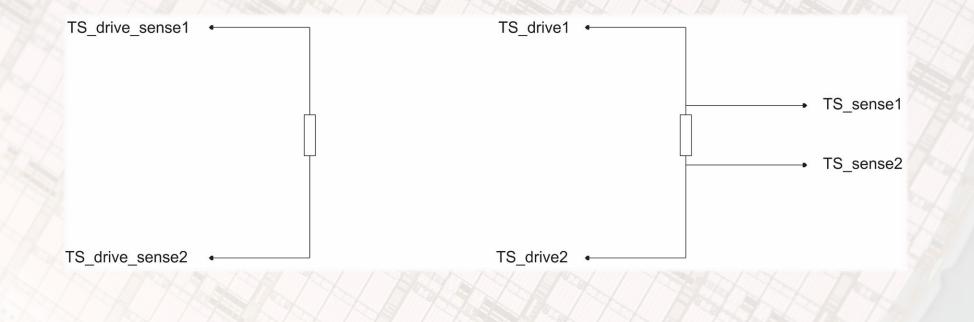

4-terminal or 2-terminal temperature sensors

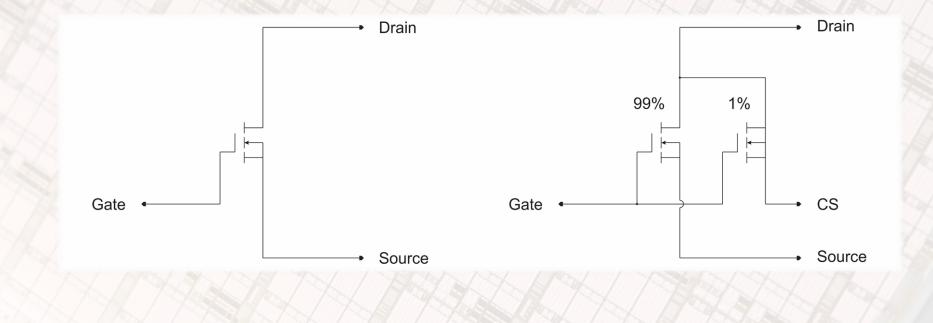

1% current-sense terminals

### Outline

- Introduction

- GaN base line technology 100V and 650V

- GaN System-on-Chip features

- GaN power HEMTs in HB configuration

- Integrated gate driver with/without levelshifters

- PWM generator

- 4-terminal or 2-terminal temperature sensors

- 1% current-sense terminals

- GaN System-on-Chip realisations and measurements

24 September 2024

24 September 2024

24 September 2024

Public

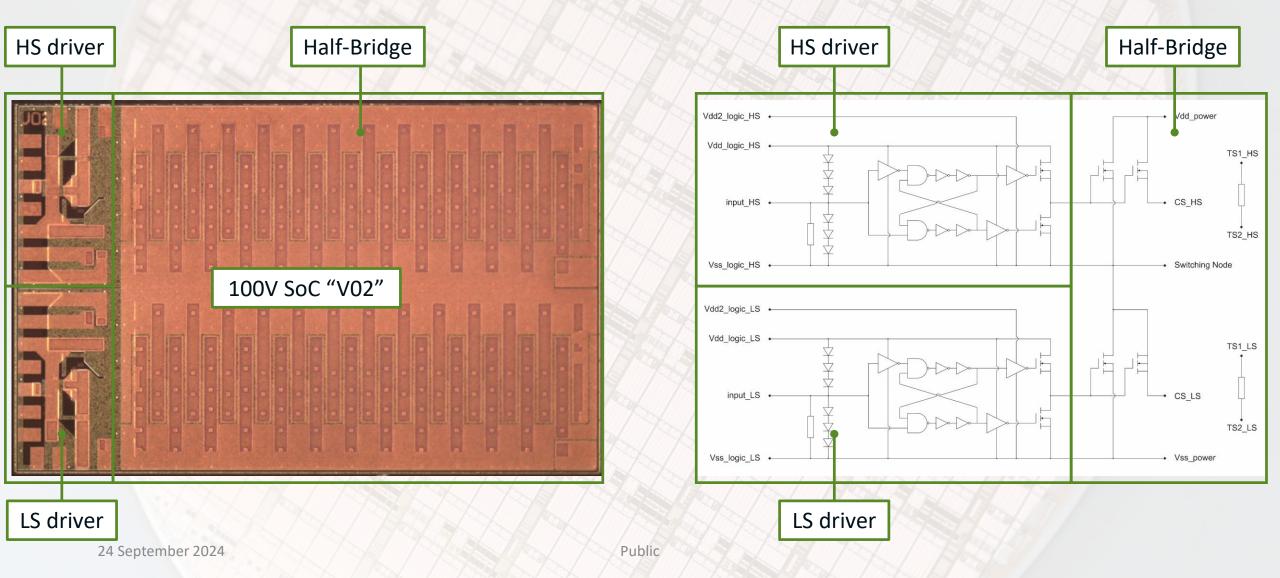

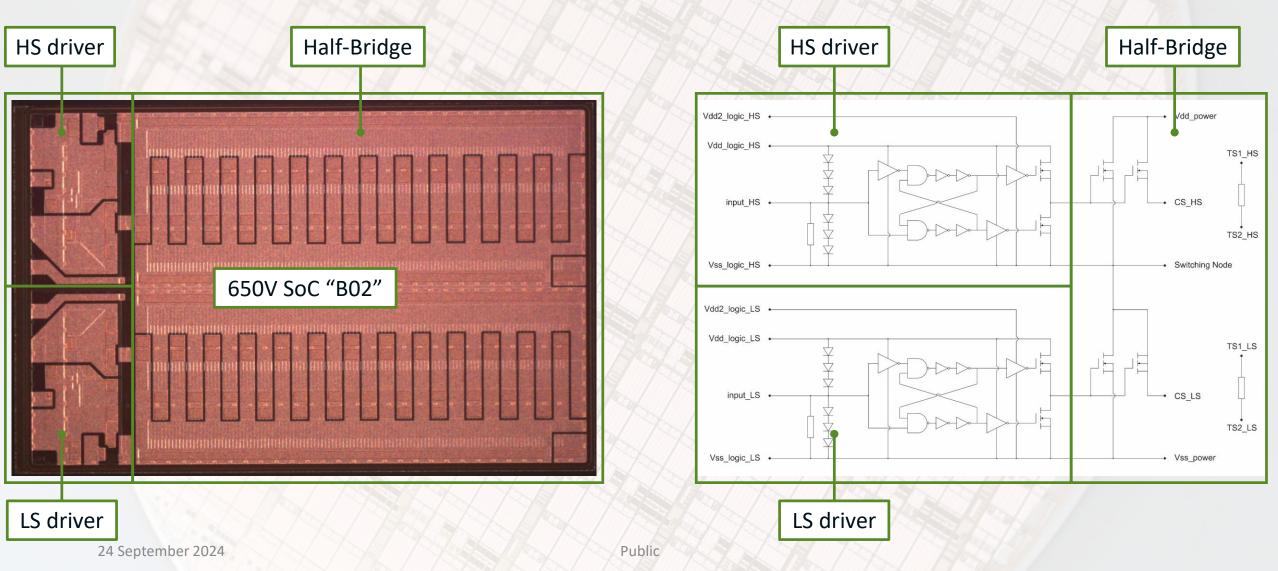

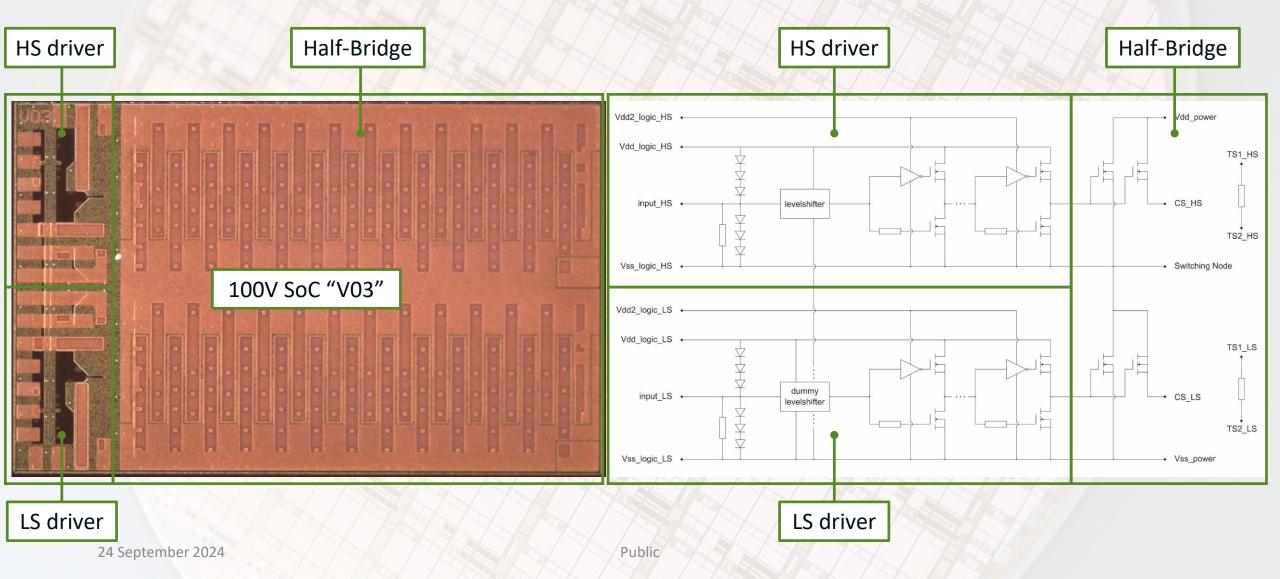

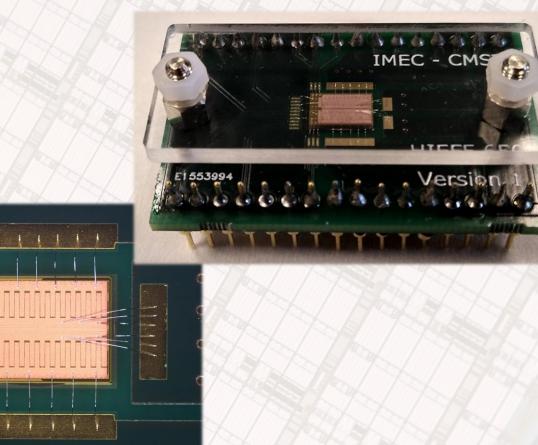

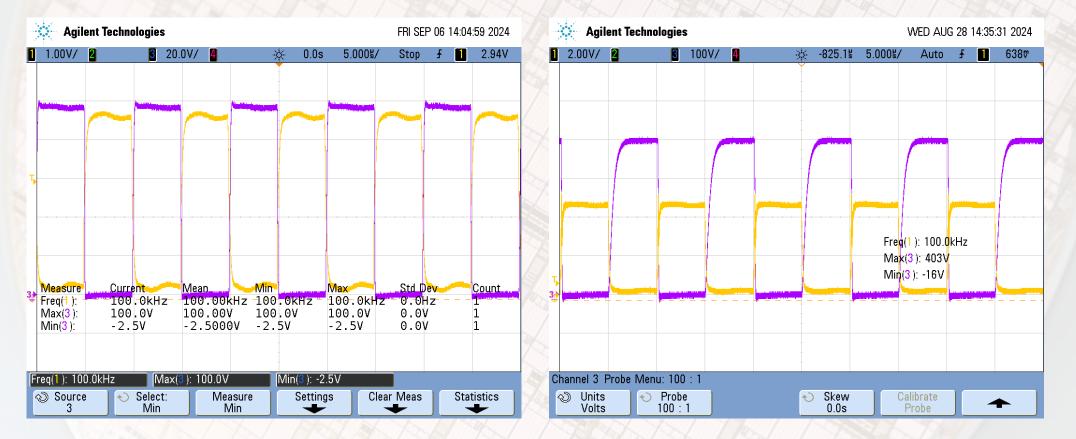

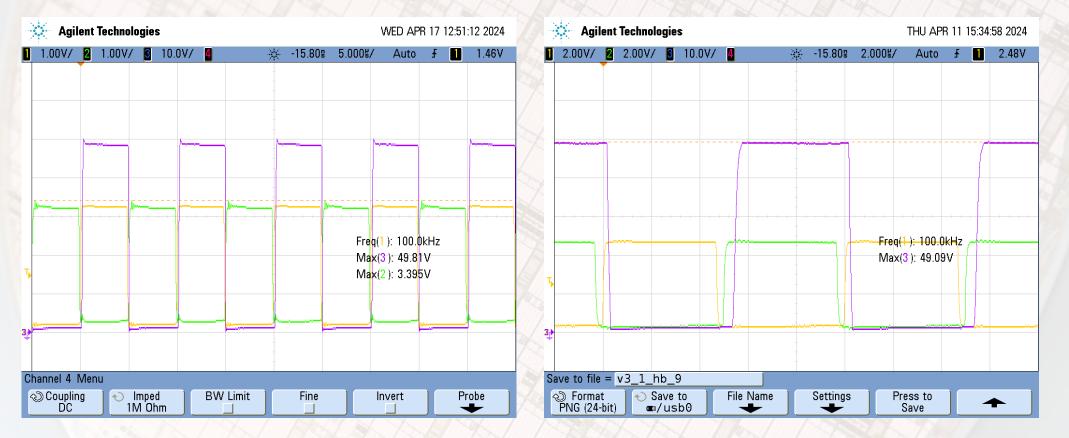

### GaN System-on-Chips measurements

- functional measurements

- SoCs wirebonded onto interposer PCB

- current-limiting resistor

### GaN System-on-Chips measurements

### • 100V SoC "V01"

• 650V SoC "V1"

### GaN System-on-Chips measurements

### • 100V SoC "S8"

• 650V SoC "V3"

End of Presentation – www.HiEFFICIENT.eu