## HI EFFICIENT

WIDE-BANDGAP TECHNOLOGIES FOR TOMORROW'S HIGHLY EFFICIENT

AND RELIABLE AUTOMOTIVE MOBILITY SOLUTIONS

# "Advances in chip embedding and its usage in a 48V inverter application"

Markus Kastelic (AT&S), Kunal Goray (AVL), Olcay Korkmaz (AVL)

This project has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No. 101007281. The JU receives support from the European Union's Horizon 2020 research and innovation programme and Austria, Germany, Slovenia, Netherlands, Belgium, Slovakia, France, Italy, and Turkey.

2008

Founded

### 950

Employees

10%

Of turnover invested in inhouse R&D **AVL** SOFTWARE AND FUNCTIONS

## Facts and Figures

100%

Integrated into the worldwide AVL network

ONE

Partner as a subsidiary to AVL List GmbH

> 30 M

Vehicles with AVL technology on the road

#### As a software and hardware developer we are leading innovation.

Global Footprint

7 engineering locations

Global customer support network

6 partner locations inside AVL

## **Company Introduction**

- AT&S World Leading High-Tech PCB & IC Substrates Company

- Founded in 1987

- Headquarter located in Leoben, Austria

- ~ 13,500 employees, 7 Locations, 12 plants

Naniangud

India

- Among the top ten PCB and IC substrates manufacturers worldwide

- Focused on Classic PCB, High-end PCB, IC substrates and Advanced Packaging

- Website: www.ats.net

Fehring

Austria

AT&S sales support office

Leoben Hinterberg

Headquarters

Austria

Chongging

China

## UC3 – 48V High Power GaN Inverter

- The objectives of this use case are

- **Reducing weight and volume** of automotive applications by reducing the converter designs by a factor of 10% and additionally enabling **unshielded cables**

- Improve efficiency to achieve a target of 98%

- Improve lifetime and reliability of the power stage and the mechanical design

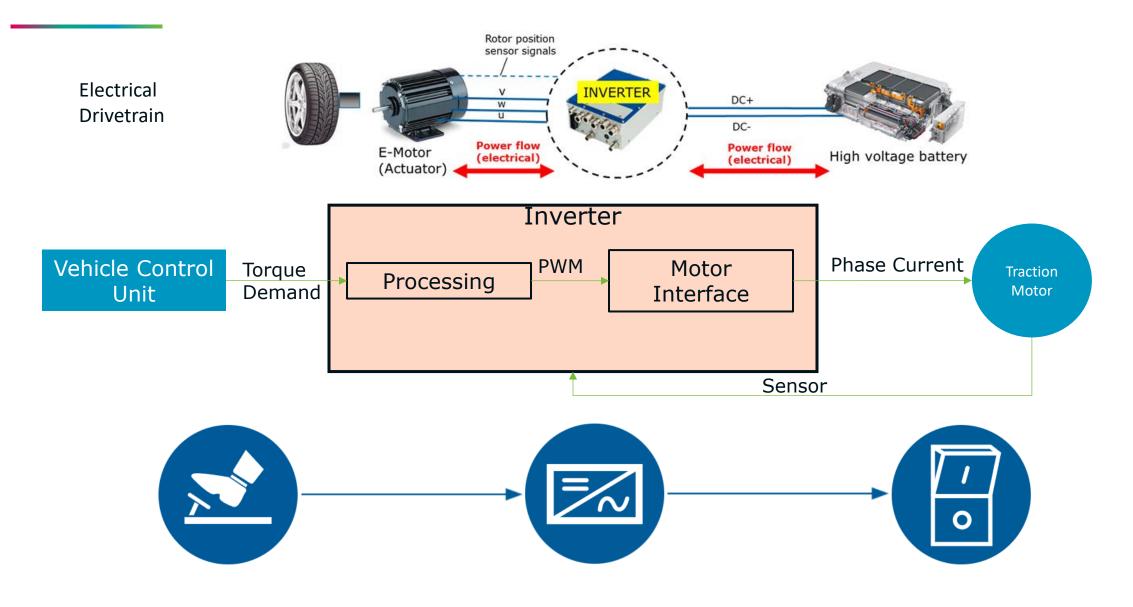

## **Traction Inverter**

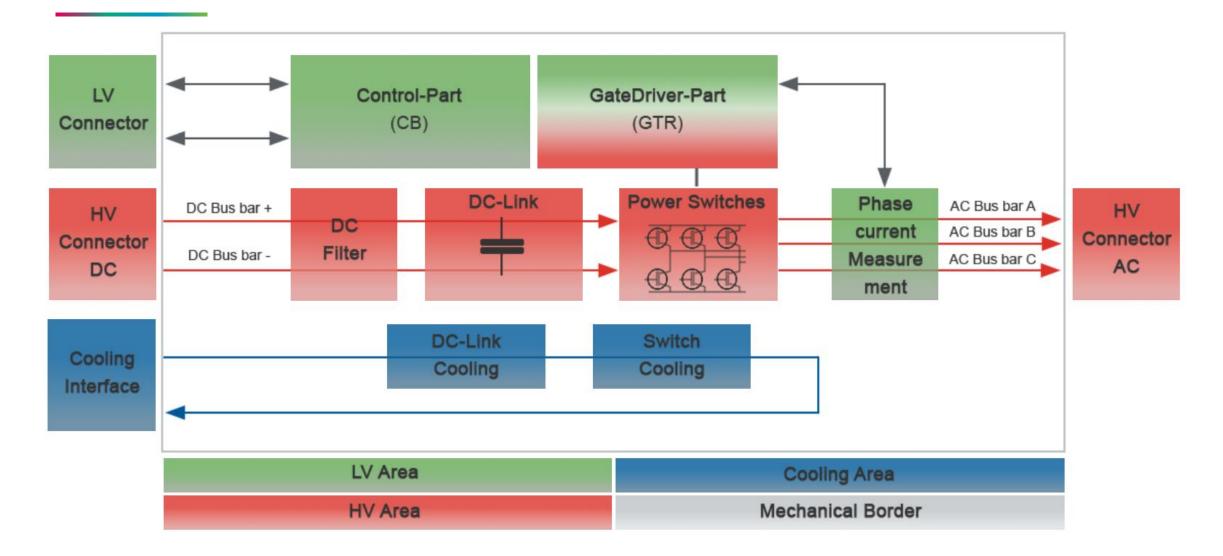

## **Inverter Architecture**

## Advantages of GaN

- Gallium nitride can conduct electrons more efficiently

- $\rightarrow$  10 times shorter switching time than Si MOSFETs

- Lower on-resistance per unit area for the same voltage rating compared to both SiC and Si

- $\rightarrow$  Lower switching loss and less EMI noise

- → Reduced size (5 to 10 times smaller than Si MOSFETs and IGBTs)

- The thermal resistance is lower than Si devices

$\rightarrow$  Better thermal performance

7

## Advantages of Embedded Die Packaging

• Shorter interconnections

$\rightarrow$  Minimizes distortion and power loss

Stable Cu interconnections

High mechanical stabil

→ High mechanical stability

- Lower thermal resistivity

→ Better thermal performance

- Design flexibility

\*https://www.microsemi.com/company/technology/embedded-die-technology

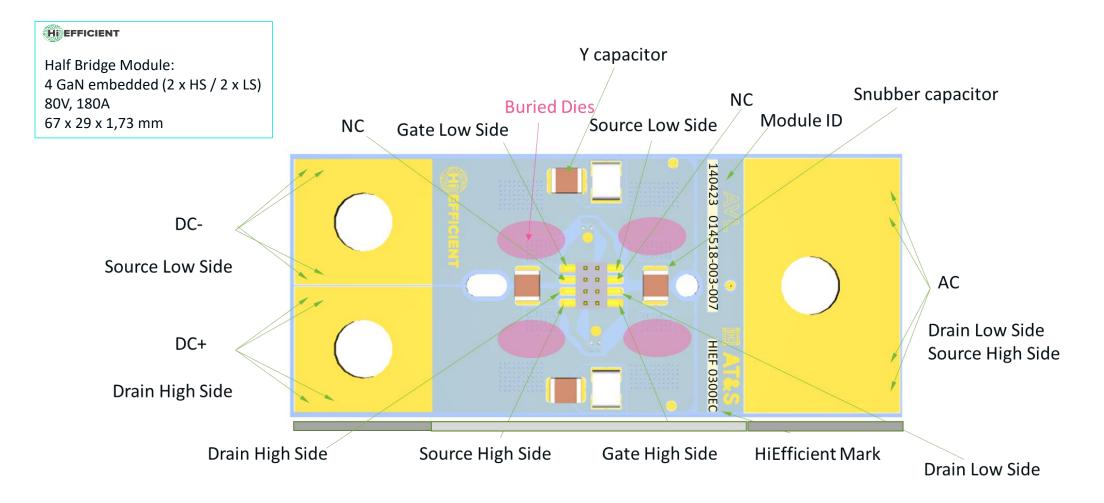

## **GaN Power Module Description**

## AT&S ECP® Technology

#### PARSEC

The preferred packaging technology for high – voltage applications with double-sided component connection and optimized thermal performance

RDL ... Redistribution Layer

| Component Type                                    | Actives – RDL mandatory                              |

|---------------------------------------------------|------------------------------------------------------|

| Min. / Max. Component Size                        | 1x1mm <sup>2</sup> – 8x8mm <sup>2</sup>              |

| Min./Max. Component Thickness                     | 150μm – 300μm                                        |

| Min. Component Pad Size /Min. Connection Diameter | Standard: 300μm / Ø150μm \\ Advanced: 270μm / Ø120μm |

| Min. Component Pad Pitch                          | Actual pad size + 100μm (sub)                        |

| Component Pad Metallization                       | Copper only                                          |

| Component Connection                              | Double-sided                                         |

| Component Fan-out Concept                         | Laser, Galvanic, Lithographic                        |

| Max. Die to Package Ratio                         | 30%                                                  |

Parsec ... Planar Surface Embedding Components

## **Sinter Lamination Technology**

Evaluation show many Ag sinter paste are compatible with Cu terminated components

Component Sinter paste Surface Diffusion Lattice Diffusion Core Grain Boundary Diffusion

ZEISS

- SEM picture Ag-sintered interfaces Ag – Cu after TCT:

- Low porosity Ag-layer

- No voiding in interface

- No delamination in interface

Mag = 10.00 K X

EHT = 10.00 kV

AT&S

Signal A = NTS BSD Date :24 Nov 2020

Time :11:41:21

WD = 10.0 mm Tilt Angle = 0.0 \*

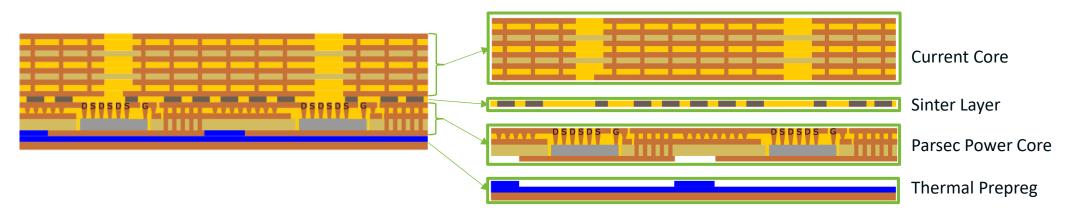

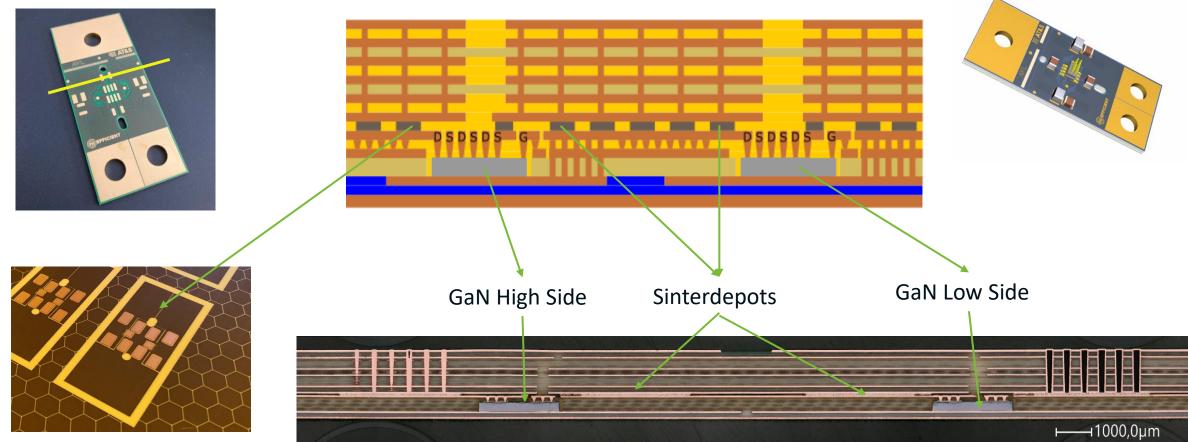

## **Construction of the Power Module**

Step 1: Parsec Power Core and Current Core are fabricated separately

Step 2: Both Cores are laminated and sintered together

Step 3: Thermal Prepreg is laminated on the bottom side

→ Reduction of parasitic inductances to enable fast switching and increase efficiency & lifetime

→ Improvement of thermal performance and Miniaturization enable higher **power density**

## **Construction of the Power Module**

**Copper based Sinter depots**

The copper based sinter lamination is a novel technology developed in HiEFFICIENT project and these half bridge modules provide the first functional demonstrators.

## Half Bridge Module

**Cross - section**

### **Static Electrical Characterisation**

| te Edit View Measurement Setup 4 |           |                         |                                  |     |           |       |        |        | ~           | * 0.1 | 200 B      | 10  |

|----------------------------------|-----------|-------------------------|----------------------------------|-----|-----------|-------|--------|--------|-------------|-------|------------|-----|

| Menurement Instrument B1564-01   | 70        | . Cl + *                | ux 🖭 🛤                           | -ff | #<br>(11) | WERN  |        | 2 63   | <u>^ 10</u> |       | -          | He. |

| · Haumare Raterys                |           |                         |                                  |     |           |       |        |        |             |       |            |     |

| Sended Parameter                 |           | Mari<br>Test Conditions | oson flatiogs                    |     |           | Volue |        | Link   | N           | Viete |            |     |

| VDS5 Draw to Service Voltage     |           | 0 °C                    |                                  |     |           |       |        | W      |             |       |            |     |

| VERS. Gate to Source Voltage     | Costman   |                         |                                  | Me  |           |       | - (X)  | × 1    |             |       |            |     |

|                                  |           |                         |                                  | Max |           |       |        |        |             |       |            |     |

| 104 Putred Deam Current          | Tex.25 *C |                         |                                  |     |           |       |        | 141    |             |       |            |     |

| ESA Pulsed Body Dudge Current    | Terzer    |                         |                                  |     |           |       |        | 14     |             |       |            |     |

| Characterizas Parameters         |           |                         |                                  |     |           |       |        |        |             |       |            |     |

| Systelaul Parameter              |           |                         | dittics Payameters<br>Conditions |     |           | Min   | Act    | Mon    | Ende        | Hote  |            |     |

| Dian Laskage Current             |           | VOS                     | 64                               | 194 | 8         |       | 36.7 4 | 2000 1 |             |       |            |     |

| Cate Leadings Correct            |           | ₩05<br>V05              | I Provedence                     |     |           |       |        |        |             |       | Street 1   | -   |

| M M Cardinal Count               |           | YUN STR                 | 1.5                              | 1   | 151       |       | 0.04   | - in   |             |       | and a      |     |

| TILL MARK Carbon Current ( )     |           | 105                     | A Partners                       |     | (a)       | 200 - | 11 and |        | 1000        |       | 1999 C 199 |     |

|                                  |           | VDS.                    |                                  | 100 |           |       |        |        |             |       | Sec. 1     | -   |

| VITTE Gen to Source Direction    |           | 10                      |                                  |     |           |       |        |        |             |       |            |     |

| Riftigent Draw to Source Do Real |           | PG D                    | 12                               |     | 100       |       |        |        | and .       |       |            | 1   |

| Contract Contract                |           | P-Ballion .             |                                  |     |           |       |        |        |             |       |            | -   |

| All Any Dear Second by           | and a     |                         |                                  |     | 8.        |       |        |        |             |       |            |     |

| Section 1                        |           |                         |                                  |     |           |       |        |        |             |       |            |     |

| Parameter           | Datasheet             | Unit                                            | Test Condition                                         | Results<br>(mean of 100 measured modules) |

|---------------------|-----------------------|-------------------------------------------------|--------------------------------------------------------|-------------------------------------------|

| R <sub>DS(on)</sub> | 1,1 max.<br>1,95 max. | mOhm (components)<br>mOhm (+Module +parasitics) | V <sub>GS</sub> =5V ; I <sub>D</sub> =50A<br>PW=500μs  | 1,44                                      |

| I <sub>DSS</sub>    | 400 max.              | μΑ                                              | V <sub>DS</sub> =64V ; V <sub>GS</sub> =0V             | 31,06                                     |

| I <sub>GSS</sub>    | 400 typ.<br>8000 max. | μΑ<br>μΑ                                        | V <sub>GS</sub> =5V<br>V <sub>DS</sub> =0V             | 4,63                                      |

| I <sub>GSS(-)</sub> | -40 typ.<br>-400 max. | μΑ<br>μΑ                                        | VGS=-4V ;V <sub>DS</sub> =0V                           | -5,51                                     |

| V <sub>GS(th)</sub> | 1,2 typ.<br>2,5 max.  | V                                               | $V_{DS}=V_{GS}$ ; I <sub>D</sub> =13mA                 | 1,39                                      |

| V <sub>SD</sub>     | 1,5 typ.              | V                                               | V <sub>GS</sub> =0V ; I <sub>F</sub> =0,50A ; PW=500μs | 1,13                                      |

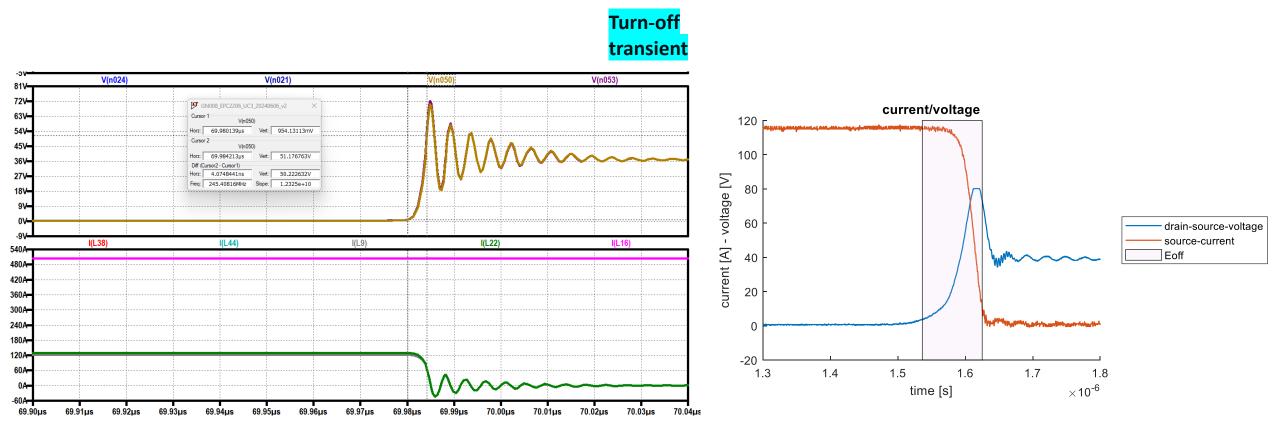

### UC 3 – DPT Simulation vs. Measurement

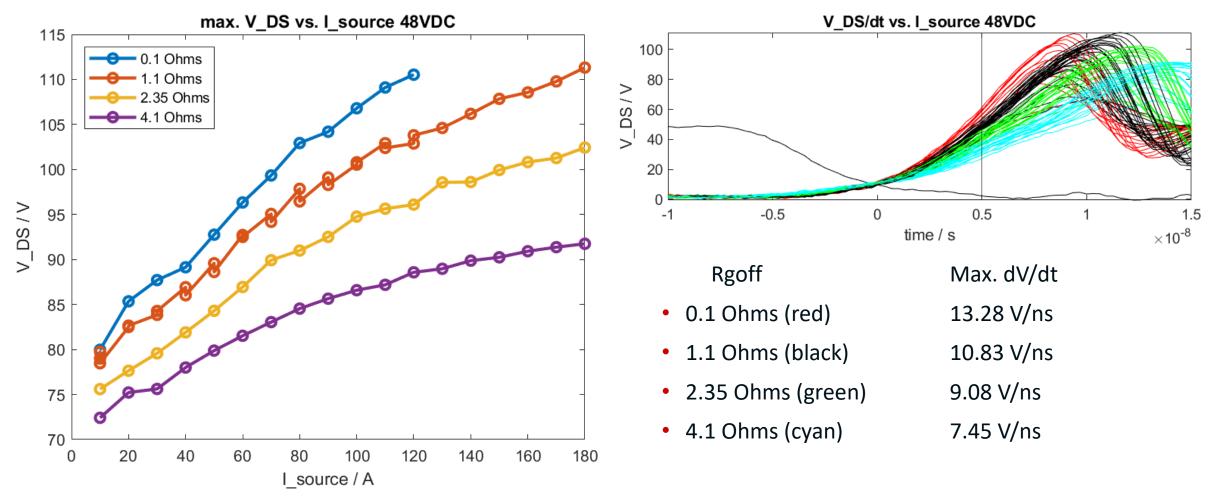

## Double Pulse Test Results/Single Module

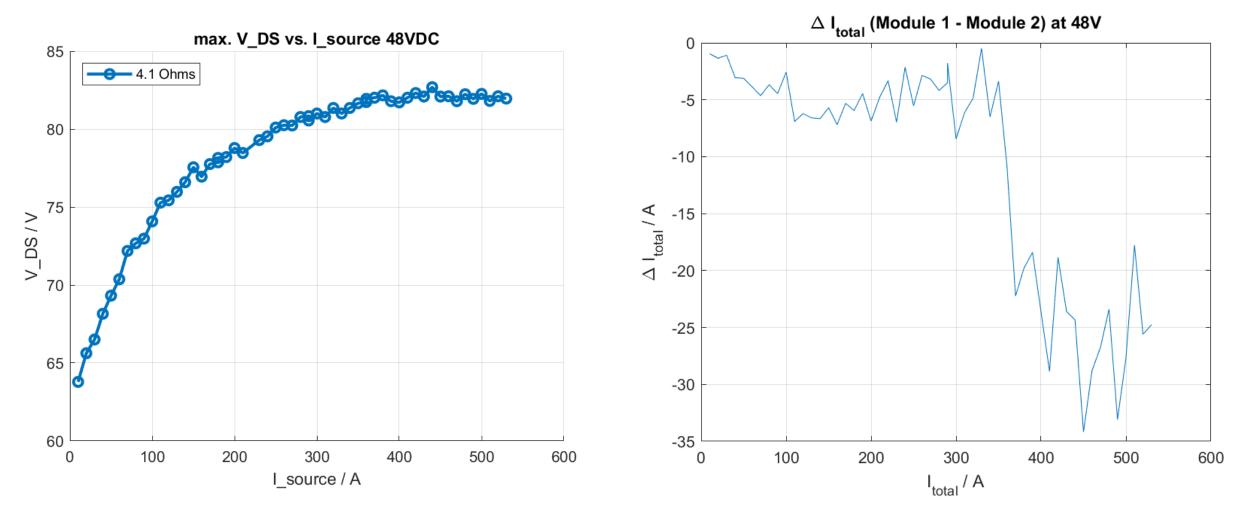

## Double Pulse Test Results/ Two Modules

8 October 2024

Public

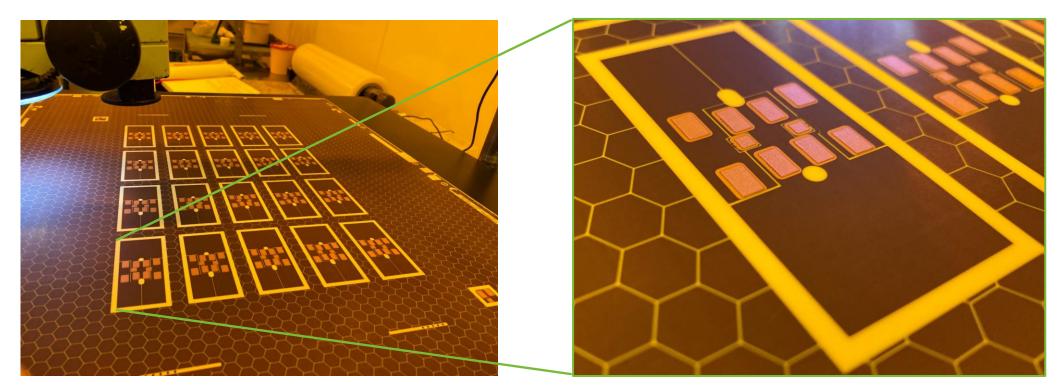

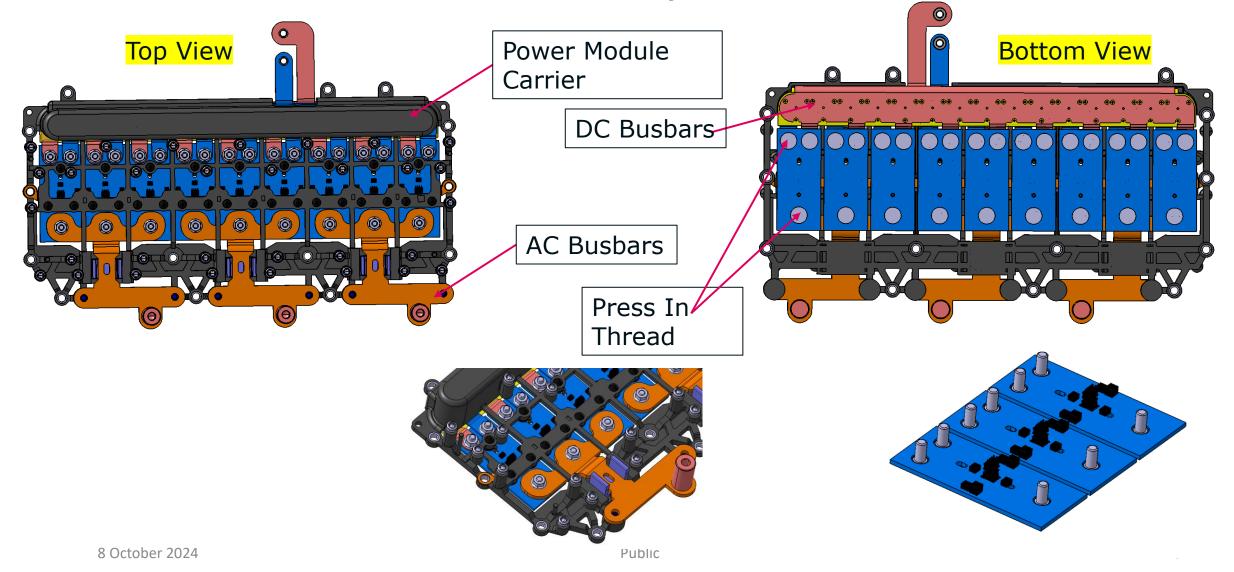

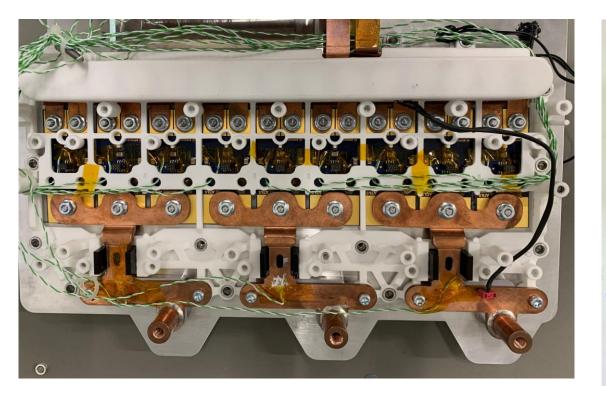

### **Power Module Assembly**

# Assembly of the Power Modules in the Inverter

End of Presentation – www.HiEFFICIENT.eu