# EVALUATION REPORT

Highly EFFICIENT and reliable electric drivetrains based on modular, intelligent and highly integrated wide band gap power electronics modules

| Project                 | HIEFFICIENT       |

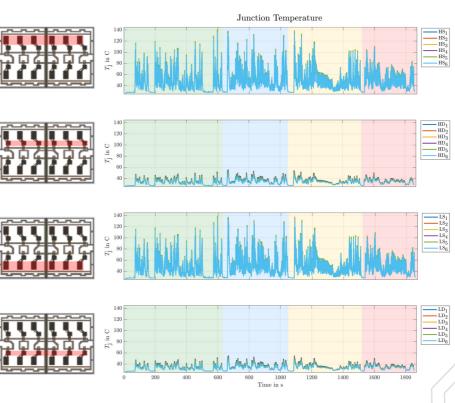

|-------------------------|-------------------|

| Grant Agreement No.     | N° 101007281      |

| Deliverable No°         | D1.6              |

| Deliverable Title       | PROJECT EVALUAT   |

| Dissemination Level     | PU                |

| Nature                  | R                 |

| Deliverable Version     | V1.0              |

| Deliverable Date        | 2024-11-06        |

| Deliverable Responsible | G. PAPAFOTIOU / C |

|                         |                   |

# ATION REPORT C. ABART

## PROPRIETARY RIGHTS STATEMENT

This document contains information, which is proprietary to the HiEFFICIENT consortium. Neither this document nor the information contained herein may be duplicated without the prior written consent of the HiEFFICIENT consortium.

This project has received funding from the Chips Joint Undertaking (JU) under grant agreement no 101007281. The JU receives support from the European Union's Horizon 2020 research and innovation programme and AUS-TRIA, GERMANY, SLOVENIA, NETHERLANDS, BELGIUM, SLOVAKIA, FRANCE, ITALY, TURKEY,

www.HiEFFICIENT.eu Copyright @ 2024 HiEFFICIENT project partners All Rights Reserved

This booklet summarises the main outcomes of the HiEFFICIENT research project - Highly EFFICIENT and reliable electric drivetrains based on modular, intelligent and highly integrated wide-bandgap power electronics modules - funded by the Chips (formerly ECSEL) Joint Undertaking (Call 2020).

Wide-bandgap (WBG) semiconductors are crucial for the advancement of the next generation of electric WP1 & WP7 Christoph Abart (AVL List GmbH) vehicles. Their superior performance over Silicon WP2 Lisa Zernig, Shaena Fischer, and Herbert Pairitsch (Infineon Technologies Austria AG) semiconductors facilitates a quicker shift towards sustainable future mobility. The HiEFFICIENT project WP3 Omar Hegazy and Gamze Egin Martin (Vrije focused on enhancing the power density and relia-Universiteit Brussel) bility of WBG semiconductor-based power electro-WP4 Hans van Dijk and Fatemeh Minaye Hashemi nic solutions for automotive applications, including (Nederlandse organisatie voor toegepast natuurweelectrified vehicles and associated charging infrastenschappelijk onderzoek) tructure. WBG materials like Silicon Carbide (SiC) and WP5 Christian Meyne (Infineon Technologies AG) Gallium Nitride (GaN) offer advantages in switching WP6 Kunal Goray (AVL Software and Functions performance, operating temperatures, and power GmbH) densities, reducing energy losses, size, and weight of power electronics compared to widely used Sili-USE CASE LEADERS con semiconductors UC1 Oliver König, Thomas Haidinger (AVL List GmbH),

The HiEFFICIENT project addressed various automotive applications through six industrial use cases, which included inverters for electric vehicles at different power levels, power electronic converters for on-/off-board charging systems, and power electronics for testing systems for electrified vehicles. A Prognostics Health Management and Reliability Framework was also developed across all use cases to ensure high reliability in respective applications. After three and a half years, almost all goals have been successfully met. This document presents the achieved results and outlines the benefits for end users.

Lastly, a heartfelt "Thank You" to all project partners for their excellent collaboration throughout the project's duration, as well as to all work package and use case leaders for managing the various work streams Project Coordinator and ensuring the project's success.

# WORK PACKAGE LEADERS

and Johannes Hammerer (AVL Set GmbH) UC2 Claudio Romano (Ideas & Motion) UC3 Olcay Korkmaz (AVL Software and Functions) UC4 Humphrey de Groot and Xinwei Xu (Heliox Energy BV) UC5 Mohamed El Baghdadi (Vrije Universiteit Brussel) UC6 George Papafotiou (TU Eindhoven)

We would also like to thank our Project Officer Anton Chichkov, who guided us very well through the project and our reviewers, Sara Giordani and Thomas Harder, for giving valuable input to our project work, helping us to improve the project outcomes.

Christoph ABART

Annemarie HAMEDLER Project Administration

Key Facts

**START** 1st May 2021, 43 Months

> **COSTS** 41 Mio €

FUNDING (EU/NATIONAL)

11.8 / 12 Mio €

# COORDINATOR

AVL List GmbH

# CONSORTIUM

31 Partners

# **TABLE OF CONTENTS**

# The Project

OVERVIEW PROJECT OBJECTIVES AND RESULTS

# Key Results

KR1 – FIRST GAN SIP AND SOC DEVICES OUT OF EUROPE KR2 – INTEGRATION METHODOLOGIES AND CONCEPTS FO POWER ELECTRONICS

KR3 – MAKE RELIABILITY AND PHM FUNCTIONS VISIBLE AT AND TO THE END USER

KR4 – ADVANCED COOLING CONCEPTS FOR HIGHLY INTEG KR5 – COMPACT AND HIGHLY EFFICIENT ELECTRICAL DRIV

# Use Cases and Achievements

towards the Objectives

UC1 – ELECTRIFICATION TEST SYSTEMS USING MODULAR POWER ELECTRONICS UC2 – E-POWERTRAIN INVERTERS UC3 – HIGH POWER 48 V DC/AC INVERTER

UC4 - MULTI-USE DC CHARGERS

UC5 - ON-BOARD CHARGERS

UC6 - MODULAR DC/DC CONVERTER FOR LOW-POWER PV

Contributors

|                          | 6        |

|--------------------------|----------|

|                          | 6<br>8   |

|                          | 10       |

| DR HIGH POWER AUTOMOTIVE | 10<br>13 |

| T THE TOP SYSTEM LEVEL   | 16       |

| GRATED POWER ELECTRONICS | 18<br>21 |

|                       | 24 |

|-----------------------|----|

| CONCEPTS AND EMBEDDED | 24 |

|                       | 38 |

|                       | 43 |

|                       | 47 |

|                       | 52 |

| / SYSTEMS             | 64 |

|                       |    |

|                       | 66 |

INTRODUCTION

# **THE PROJECT**

The HiEFFICIENT project was initiated in 2021 as a continuation of the HiPERFORM project, which pioneered the use of wide-bandgap (WBG) technologies in electronic power circuits for electrified vehicles and charging infrastructures. Building on its results and insights, the HiEFFICIENT project aims to enhance integration and reduce volume at all levels, from die to system level. It also focuses on improving efficiency and extending lifespan through advanced sensing and control technologies.

With a holistic approach, 31 consortium partners from 9 different countries represent the entire supply chain, ranging from semiconductor up to vehicle manufacturers.

The project addressed developments along the whole value chain by

- designing new power devices and switches

- integrating power devices and switches into sub-systems and

- evaluating the newly developed devices on system level in six industrial use cases and more than 10 tech-• nology demonstrators.

The industrial use cases included the deployment of WBG power devices in various EV applications such as traction inverters with different power levels, both off-board and on-board charging solutions, and modular power electronics for electrified vehicle testing systems. The specific use cases and their respective leaders are detailed below:

# UC1 - ELECTRIFICATION TEST SYSTEMS (AVL List GmbH)

Development of highly compact and reliable test and emulation systems for electric components in electric vehicles using latest SiC and GaN technology.

# ding technologies.

# UC3 - HIGH POWER 48 V DC/AC INVERTER (AVL Software and Functions GmbH)

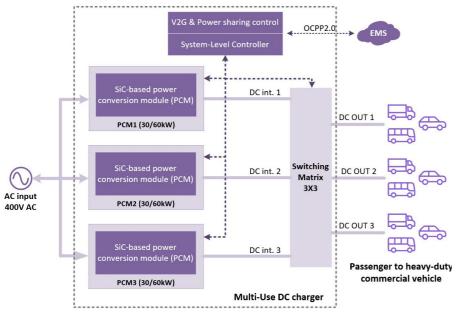

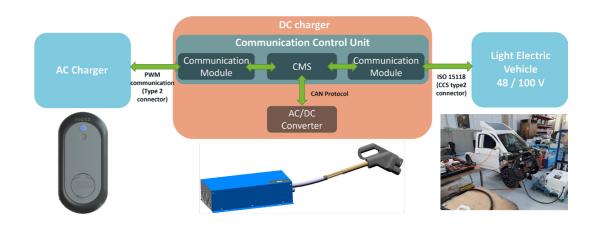

# UC4 - MULTI-USE DC CHARGER (Heliox Energy BV)

Development of bidirectional, flexible multi-output off-board charger, which aims to accommodate different charging needs for different e-mobility devices.

# (TU Eindhoven)

# UC2 - E-POWERTRAIN INVERTERS (Ideas & Motion)

Development of two traction inverters, having a focus on fail safe multi-drive powertrain application and on highly integrated powertrain inverter, using power electronics embed-

Investigation of the benefits of a highly compact 48 V inverter for use in long-haul heavy duty vehicles. Focus is on the package density and improved reliability.

# UC5 - ON-BOARD CHARGERS (Vrije Universiteit Brussel)

Demonstration of different power electronic converters for on-board chargers, featuring a more compact system, high efficiency, high power density and integration with other auto-

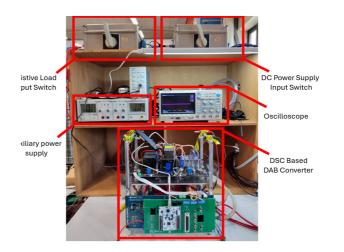

# UC6 - MODULAR LOW-POWER DC/DC CONVERTER FOR LOW-POWER PV SYSTEMS

Development of DC/DC converter for photovoltaic (PV) applications and benchmarking latest 100 V GaN devices developed in HiEFFICIENT.

# **PROJECT OBJECTIVES**

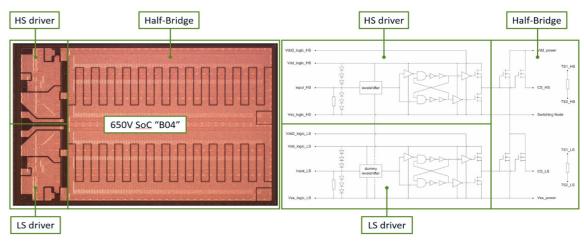

In the HiEFFICIENT project, significant progress was made towards ambitious objectives improving power electronic efficiency, increasing power density and lifetime of power electronics. This was enabled by developing new GaN devices, demonstrating a 650 V GaN System-on-Chip half-bridge device on one single piece of semiconductor as well as new integration technologies like power electronics embedding in the printed circuit board. Various demonstrators showcased these achievements, each contributing to specific goals.

# **OBJECTIVE 1: INTEGRATION AND VOLUME REDUCTION**

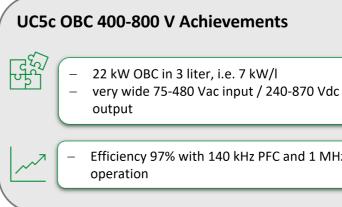

HiEFFICIENT started with the vision to demonstrate the potentials and limitations of integration technologies at various levels, be it at on component (e.g., System-on-Chip, Systemin-Package), subsystem (e.g., embedding power electronics components in printed circuit boards) and system level (e.g. on-board-charger and DC/DC converter integration) to achieve a significant volume reduction of up to 40%. First, HiEFFICIENT partners succeeded in developing most compact 100 V GaN System-in-Package devices, having a half-bridge configuration, being about 15% more compact than comparable state of the art solutions at this point in time (12/2022). Some passives could be integrated additionally, which enabled excellent switching behaviour without increasing the volume. Furthermore, first time a 650 V System-on-Chip half-bridge device on one single piece of semiconductor has been developed, and this is still unique for today's available devices. The expectation for the future is, that full SoC integration will lead to better controllable parasitic inductances, which will decrease ringing issues and overshoots. Another leap forward was made with embedding power electronics components in printed circuit boards. This led to a volume reduction of up to 19% compared to SMD based solutions. Additionally, the overall size of an embedded half-bridge SiC module compared to a classic power module was reduced by 30% in area and 50% in volume. On system level, significant advances have been made by driving widebandgap devices towards today's limits. So, a power density increase of a power converter by a factor of 2 compared to the baseline has been achieved. Furthermore, an OBC with more than 7 kW/l is demonstrated, outperforming the SOTA of 4 kW/l by a factor of 1.75, relating to around 40% volume reduction. All in all, the set objective was entirely achieved.

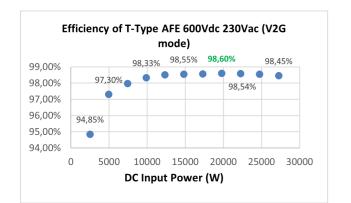

# OBJECTIVE 2: INCREASE EFFICIENCY AND REDUCTION OF LOSSES

When developing power electronics, efficiency and reduction of losses is key to increase driving ranges and decrease total costs of ownership of future electric vehicles. Hence, almost all use cases in this project had a focus on increasing efficiency and reducing losses in the respective applications. Therefore, efficiencies greater than 98% and 50% reduction of losses were targeted.

One key focus of the project was to enhance loop inductance through embedding technologies and advanced packaging, thereby minimizing parasitic losses and improving efficiency. The prototypes developed demonstrated notable improvements, achieving up to 50% better performance, depending on the specific package or module being compared. The measured stray inductances decreased to as low as 3.4 nH, compared to similar state-of-the-art power modules that measure 8 nH. These improvements contributed to the design of highly efficient converter systems, achieving peak efficiencies up to 98%.

Other development aspects have been on the optimization of low-level control strategies and active gate driver (AGD) networks to improve efficiency. Project partners could demonstrate the benefit of Discontinuous Pulse Width Modulation (DPWM) compared to standard Space Vector PWM (SVPWM) showing up to 3% efficiency improvement in low speed and low torque regions of an inverter application. In case of AGDs 15-20% lower turn-on losses have been achieved.

Objective 1

Integration and volume reduction

Objective 2

Increase efficiency and reduction of losses

Objective 3

Lifetime improvement

Objective 4

Intelligent power modules

#

# **OBEJCTIVE 3: LIFETIME IMPROVEMENT**

The HiEFFICIENT project achieved significant advancements in Reliability and Prognostic Health Management (PHM) for power electronic converters, targeting a lifetime enhancement of 20%. The project investigated lifetime enhancements from component to system level. At component level, efforts have concentrated on improvements in chip packaging, i.e., novel chip embedding concepts in the PCB. Therefore, advanced multi-physics simulations have been conducted, including complex electro-thermal and thermo-mechanical analyses. The developed solutions showed significant improvements with respect to loop inductance (up to two times), switching overshoots (up to 15%) and switching speed (up to 30%), consequently leading to higher efficiencies while ensuring higher margins for junction temperatures to maximize component lifetime. Furthermore, it could be proven that a significant increase in robustness is possible based on this packaging concept (50 times longer lifetime). Another focus was on data-driven and hybrid PHM methods. By analysing key packaging related failures such as bond wire lift-off and die attach degradation, newly developed methods have been integrated in innovative control algorithms and realtime monitoring systems for predictive maintenance, meeting reliability targets. Additionally, Design for Reliability concepts have been followed, to reach for a multi-use DC charger Mean Time Between Failures (MTBF) of over 150,000 hours, representing a 50% improvement in MTBF. Finally, a novel power electronics lifetime testing setup has been developed, confirming the feasibility to assess series failure rates of power electronic components, e.g., inverters. Overall, HiEFFICIENT successfully enhanced power electronics reliability, directly addressing critical technology bricks for improved thermal management, failure prevention, and extended system lifetimes.

**OBEJCTIVE 4: INTELLIGENT POWER MODULES**

WBG semiconductors enable applications and systems with increased power density, faster switching, and higher operating temperatures compared to Silicon semiconductors. Accelerated switching has great potential to reduce losses, but it often comes with increased current overshoot and parasitic ringing. Therefore, different concepts to enhance the performance of the power electronics have been investigated. They showed significant advances for future applications, and a few examples are highlighted in the following. One approach followed was the development of an active gate driver (AGD) network to achieve a faster turn-on switching transient and to reduce the turn-on switching losses without increasing the parasitic ringing and current overshoots. The developed AGD allows simple integration into existing designs, specifically not requiring any modifications of the controller. Measurement results demonstrate that 15-20% lower turn-on losses can be achieved without increasing parasitic ringing and current overshoots. Further an adaptive gate driver has been developed to control the gate voltage actively. This enables the control of the junction temperature of SiC MOSFETs by manipulating the conduction losses and hence, reduces the thermal cycling of the power switches. Lastly, a generative adversarial network temperaturedependent thermal model has been developed, to estimate SiC die junction temperatures. Thereby a temperature sensing bandwidth of 20 Hz has been achieved. This is a significant advance compared to traditional systems, which often operate below 10 Hz. This higher bandwidth enables more accurate and faster thermal monitoring of the power semiconductors.

# **FIRST GAN SIP AND SOC DEVICES OUT OF EUROPE**

# INTRODUCTION

Gallium Nitride (GaN) System-on-Chip (SoC) and System-in-Package (SiP) solutions represent a significant advancement in power electronics, combining the high efficiency and fast switching capabilities of GaN technology with the integration benefits of SoC and SiP designs. These solutions integrate multiple functions, such as power control (i.e., gate driving circuitry) including possible sensing functionality (i.e., current and temperature sensing) and power conversion into a single chip, reducing the overall system size and complexity. In this project, two different voltage ranges were targeted in case of SoC designs: 100 V and 650 V, using imec's technologies. The 100 V SoC in HiEFFICIENT was designed and developed in the baseline GaN-IC technology on GaN-on-SOI substrates; whereas the 650 V SoCs were developed using the baseline 650 V baseline GaN-IC technology on GaN-on-poly-AIN (engineered) substrates. Two learning cycles were designed, yet only the SoCs of learning cycle one went to the embedding processing and to the UCs. The second learning cycle SoCs were tested by imec for their functionality only, since advanced packaging allowing for power conversion was not available within the time frame of HiEFFICIENT.

Secondly, SiP devices by Infineon were developed, integrating in a half-bridge laminate package module 2x100 V 3 mOhm CoolGaN HEMTs, a half-bridge driver with integrated bootstrap diode, high-frequency bypass capacitors, gate resistors, and a bootstrap capacitor.

## PROGRESS BEYOND STATE OF THE ART

The current landscape of GaN technology features mainly Systemin-Package (SiP) solutions and just a few System-on-Chip (SoC) solutions from various leading companies. Navitas Semiconductor offers GaNFast<sup>™</sup> power ICs, which are highly integrated SiP solutions combining GaN power FETs with drive, control, and protection circuits within a single package. Efficient Power Conversion (EPC) provides true SoC solutions with their eGaN® ICs, such as the EPC2152, which integrates GaN FETs with drivers and level shifters on a single die, targeting 100 V applications. Innoscience provides highly integrated SiP solutions like the ISG3201, which integrates two 100 V 3.2 mOhm e-mode GaN HEMTs with driver circuitry, but it is not a true SoC. Vanguard International Semiconductor (VIS) and ST Microelectronics offer highly integrated GaN solutions, but these are typically SiP rather than true SoC. VIS's 650 V GaNon-QST technology and ST's MasterGaN family combine GaN transistors with drivers and protection circuits within a single package, suitable for high-power efficiency applications.

Overall, while true GaN SoC solutions are emerging, many companies still rely on SiP technology to achieve high levels of integration and performance across various voltage classes and applications.

In HiEFFICIENT, imec demonstrated true monolithic integration of a full half-bridge and gate driving circuitry and this for both 100 V  $\,$ and 650 V. The size of the power switches on these SoCs had

to be limited in order not to end up with too large footprints, yet competitive on-resistance values could be reached.

Furthermore, Infineon demonstrated most compact 100 V GaN System-in-Package devices, having a half-bridge configuration, being about 15% more compact than comparable state of the art solutions worldwide.

## TANGIBLE RESULTS

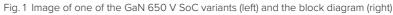

During the HiEFFICIENT project, two learning cycles were completed for each voltage range up to the functional measurements of the SoCs. This results in 4 different full reticle designs that were drawn and used in several device lots. Each of these designs contained several SoC variants changing in complexity ranging from simple half-bridge (two power switches without any additional circuitry) to halfbridges with low-side and high-side gate drivers, level shifter, low-side and high-side temperature sensors, protection diode-connected HEMTs at the terminals, pull-down resistors, and low-side and high-side current sensors. An example of such an advanced half-bridge with integrated circuitry is shown in Fig. 1.

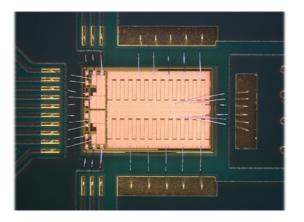

Functional test measurements were carried out by imec as seen in Fig. 2. Several SoCs (both for 100 V and 650 V and from both learning cycles) were already tested and proven to be functional. Of course, these functionality tests are limited in current (and voltage for the 650 V), and switching frequency as the wire bonding of the SoC to the test interposer board is not an ideal power application solution. For the second learning cycle design, the targeted on-resistance values for the power switches on the SoCs were as low as 8 mOhm (100 V SoCs) and 105 mOhm (650 V SoCs), with current levels targeted at 125 A and 16 A, respectively.

Fig. 2 One of the SoCs wire-bonded towards an interposer board for functionality testing (left). Result of one such functionalitv test (right)

# **KEY RESULTS**

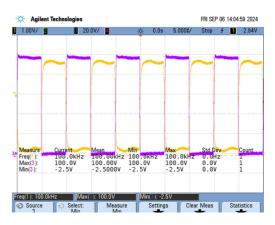

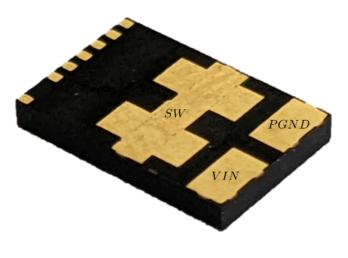

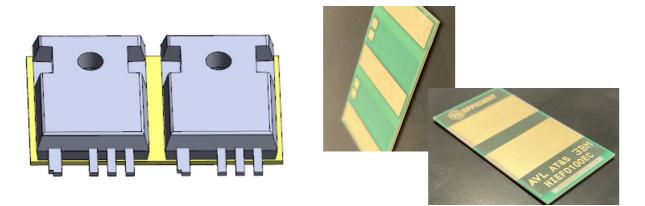

Infineon has successfully integrated current and temperature sensors within the GaN HEMT device to improve future SoCs which can be integrated in a SiP (for example temperature sense and current sense on a SoC and the driver together with the SoC in a SiP). Thus, enabling protection against over-current peaks, short circuit events, and operations outside the safe operation area. This is crucial as a 3 mOhm transistor which can deliver 400 A during a short circuit. A novel current sensor was developed in the HiEFFICIENT project, while the initially proposed temperature sensor based on 2DEG temperature dependency lacked accuracy. A new Schottky diode temperature sensor was developed, providing high accuracy of +/- 5 degrees Celsius. Finally, demonstrators (cf. Fig. 3 and Fig. 4) of a half-bridge laminate package module are integrating

- 2x 100 V 3 mΩ CoolGaN HEMTs,

- 1x half-bridge driver with integrated bootstrap diode,

- high-frequency bypass capacitors,

- gate resistors, and

- bootstrap capacitor.

The module enabled a solution with all essential passives integrated. Moreover, the solution simplifies the system layout and allow the designer to focus only on the system layout optimization. Consequently, this module reduces the overall system cost and time-to-market.

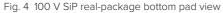

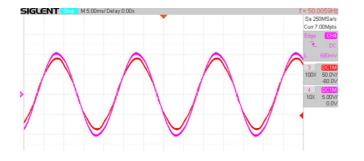

Preliminary tests have been carried out at Infineon side to verify the basic features of the half-bridge module and the ease-of-use of the module could be verified in application later. Especially the external circuit immunity (Fig. 5) showed an excellent behaviour because of the integrated passives.

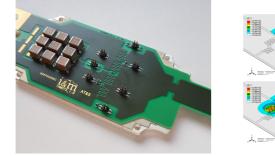

Fig. 3 3D top view inside package of 100 V SiP

Fig. 5 Preliminary experimental concept validation: external circuit immunity

# INTEGRATION **METHODOLOGIES AND CONCEPTS FOR HIGH POWER AUTOMOTIVE POWER ELECTRONICS**

## INTRODUCTION

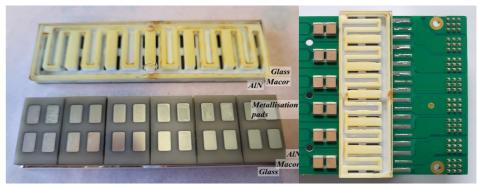

To improve the efficiency in modern cars on the way to electro mobility, the power density has to increase without limitations on performance and reliability. New module concepts with wide-bandgap semiconductors are the best candidates to face these challenges. First priority is on thermal management and handling of high current. This requests reduction of inductance and switching losses. The implementation of power semiconductors like MOSFETS, IGBTs, or diodes directly into the printed circuit board (PCB) is a very promising approach to fulfil these requirements. AT&S successfully used the expertise with its ECP (Embedded Components Packaging) technology for the implementation of efficient power packages and modules. This made it possible to reduce the space required for power packages by up to 50% with correspondingly higher power densitv.

## PROGRESS BEYOND STATE OF THE ART

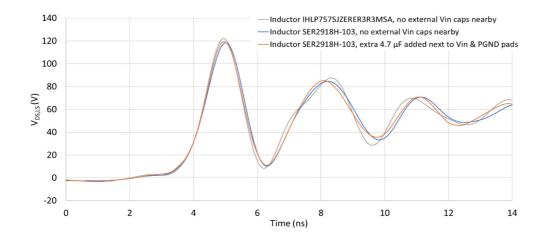

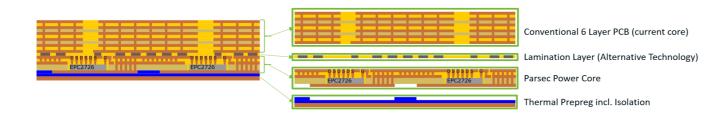

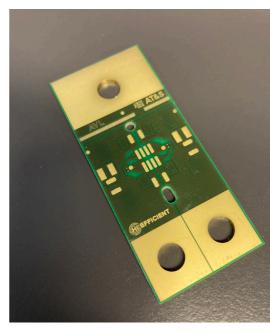

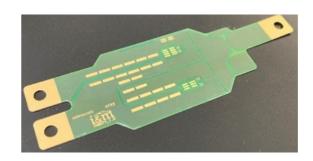

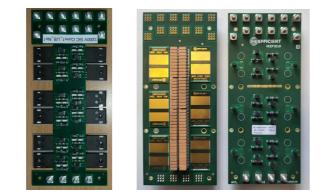

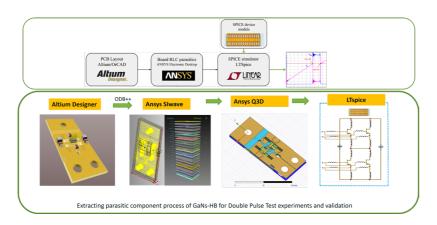

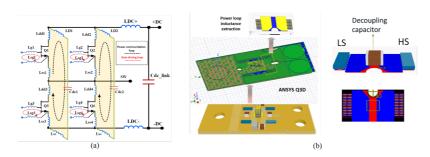

In this project AT&S investigated in development of novel Target for the embedded variant was to reduce size and to optimize integration concepts and interconnect technologies. Therefore, electrical performance. The module consists of two SiC MOSFETs different embedding concepts to realize power modules with (1 for high side and 1 for low side), which are integrated with integrated discrete SiC devices (UC1), discrete GaN devices (UC3) embedding technology into the inner core. The build-up consists and the novel GaN SoC devices (UC2b and UC5a) were designed of 5 layers. To provide isolation on the back side of the module and manufactured and improve thermal performance, a thermal prepreg is provided In relationship to UC1, the build-up of a half-bridge module between layer 4 and 5. The front side provides all the functional is visualized in Fig. 1. The heart of this build-up is a so-called connections for gate and source sense for high side as well as low PARSEC-power core with the embedded active components. The side and includes connections for DC+, DC- and switched node.

connection to the component is done by µvia on front side (gate, source) and with direct copper attach on the backside (drain) which

is realized by using a galvanic copper process.

Fig. 2 TO-247 Reference half-bridge left versus embedded module right

As shown in Fig. 2, embedding of SiC bare dies for a half-bridge solution enables a significant reduction of the volume by up to 80%, especially reducing the height to less than 20%. Additionally, an analysis of the loop inductance showed an improvement of 50% for the embedded solution, which enables the possibility of higher switching frequencies.

Furthermore, the development on sinter lamination technology was investigated with different sinter paste materials to be compatible with embedding concepts. In addition, a further objective was to develop embedding and its modifications to enable integration of GaN bare dies realizing higher electrical and thermal performance. Therefore, a GaN based power module using sinter lamination technology for increased current carrying capability was designed and fabricated. As shown in Fig. 3 a PARSEC core and additional a current core are fabricated independently. The PARSEC core consists of two GaN dies in parallel for high side and for low side, the current core is a conventional 6-layer PCB. After fabrication of the 2 cores, the interconnection between them is then realized by copper depots which are sintered during the lamination process (sinter lamination) and, in a last step to provide isolation and increased thermal performance, a thermal prepreg is used on the backside of the module. The size of one half-bridge module is l×w×t = 67×29×1.73 mm.

## Fig. 3 Schematic build-up of the UC3 power module

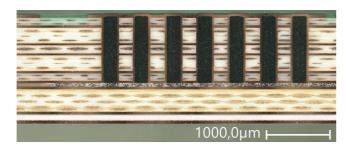

The sinter lamination is a novel technology developed in this project and implemented to provide the first functional demonstrators. The alternative connection layer improves the current carrying capability as well as the thermal behaviour for the connection of the two cores. Fig. 4 shows the printed Cu-paste during fabrication and Fig. 5 shows a cut of the finished half-bridge module (whole stack-up including the sintered Cu-Depot).

Fig. 4 Printed Cu-paste depots UC3

Fig. 5 Full stack-up showing sinter lamination layer including the sintered Cu-paste.

Fig. 6 Half-bridge module

Fig. 7 Cross section of the half-bridge module

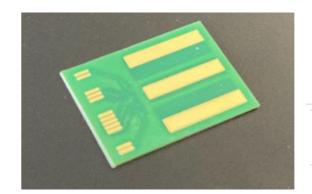

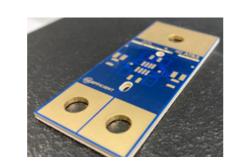

Fig. 8 650 V GaN SoC module

Fig. 9 Single 650 V SoC package

HIEFFICIENT

Fig. 6 shows the module after fabrication and Fig. 7 shows the cross section of the low-side of the module. In the cross section, the two parallel low-side GaN HEMTs with front side  $\mu$ Via connection and direct galvanic copper attach on back-side can be seen.

Further, the newly developed 650 V GaN SoC on polyAIN was embedded in the PCB, following two different concepts (Fig. 8, Fig. 9). One concept focused on a power module, having 2 SoCs embedded in parallel by using a PARSEC core and fabricated as an unsymmetrical 3-layer module. The second concept was a single packing of the SoC for further use, comparable to a conventional SMD packaged component.

# TANGIBLE RESULTS

By applying embedding technologies significant advances in volume reduction and increasing voltage limits of embedded dies have been demonstrated. In case of the 1200 V SiC half-bridge module, a benchmark compared to the STMicroelectronics SiC Module used in the Tesla Model 3 shows a volume reduction by 75% possible, even if it is rated with lower voltage, but comparable current.

In case of the developed GaN power modules, even a higher volume reduction greater than 90% could be achieved. As a benchmark, a 650 V, 300 A, 3-phase GaN power module (GS-EVM-3PH-650V300A-SM1) was considered for comparison of the 650 V GaN SoC power module developed in HiEFFICIENT.

Besides the volume reduction, also the embedding process could be enhanced by applying sinter lamination techniques using Cu-paste and hence improving the thermal performance of the package.

Another important aspect is a significant enhancement in reliability compared to the conventional packages. This is described in more detail in the key result "Make Reliability and PHM functions visible at the top system level and to the end user".

INTRODUCTION

# MAKE RELIABILITY AND PHM FUNCTIONS VISIBLE **AT THE TOP SYSTEM LEVEL** AND TO THE END USER

Fig. 2 Surrogate models for electro-thermal-mechanical fatigue assessment

Reliability on the one hand and in-depth knowledge of the health status of power electronic devices on the other are crucial to ensure customer acceptance, confidence, and sustainability of tomorrow's power electronics for electric vehicles. Key areas covered in HiEFFICIENT include the development of tests as well as the run of tests for new power modules, the application of Prognostic Health Management (PHM) and multi-physics models for real-time system assessment, and innovative strategies for thermal management and failure analysis. These efforts aim to push the boundaries of current technologies to ensure greater durability and operational efficiency in power electronics systems that are critical to a wide range of industrial and automotive applications. Each demonstrator delivered specific outcomes and technological breakthroughs that contribute to the overall goal of improving system reliability and performance through cutting-edge research and collaboration.

# PROGRESS BEYOND STATE OF THE ART

Significant advancements were achieved within HiEFFICIENT, focusing on enhancing the reliability and operational efficiency of power electronics systems through Prognostic Health Management (PHM), condition monitoring, and extensive lifetime testing. Each demonstrator has contributed uniquely to the overarching goal of improving system robustness and performance in industrial and automotive applications.

# PHM

Different PHM approaches have been investigated. One comprehensive approach focused on developing a smart multidrive unit that incorporated a PHM method applied to dual inverters. This included the utilization of reliable State of Health (SoH) estimation

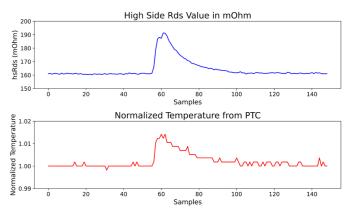

methods that are both data-driven and based on physics of failure models. The project also introduced first time a hybrid approach that combines data and physics-based methods for assessing the health state of traction inverters, significantly improving the system's fail-safe capabilities and maintenance strategies. Another development targeted a PHM circuit designed to measure Temperature-Sensitive Electrical Parameters (TSEPs) (i.e., on-state voltage, current and on-state resistance), integrating noise removal techniques to ensure accurate data correlation, as shown in Fig. 1. The effectiveness of the circuit in tracking changes in junction temperature showcased its potential as a crucial element in PHM methodologies, enhancing the predictive maintenance capabilities of power electronics systems.

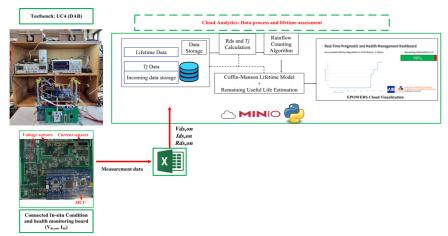

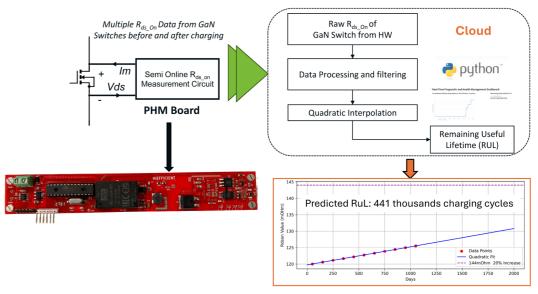

Fig. 1 Cloud-connected in-situ PHM implementation for UC4 including TSEPs measurement hardware and lifetime assessment framework

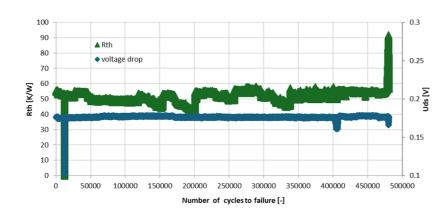

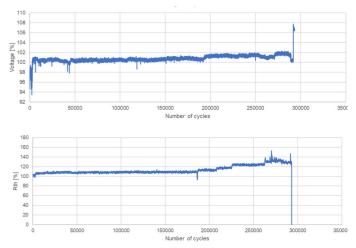

Moreover, another demonstrator focused on assessing the lifetime cycles, while the 650 V dies reached 490,000 cycles under harsh of GaN switches by developing a PHM to measure the R<sub>dean</sub> before conditions without failure. Further, 1200 V SiC dies have been embedded in half-bridge configuration in a PCB, which already each charging cycle. This approach provided a precise, real-time assessment of the switch's condition, demonstrating a proactive exceed 500,000 cycles without electrical degradation under controlled load conditions - and still counting. These tests were method for predicting component lifespan based on continuous data monitoring. complemented by detailed mechanical and thermal simulations, as Condition Monitorina well as physical failure analyses, to understand the stress effects With respect to condition monitoring, the project partners explored on power modules

the implementation of condition monitoring in power electronics used in electrification test fields. Techniques such as using gate TANGIBLE RESULTS drivers to maintain constant losses, employing non-invasive Overall, the collaborative efforts across the project have led to groundbreaking developments in PHM, condition monitoring, temperature measurements to adjust system performance, and applying data-driven methods to assess system health were and lifetime testing for wide-bandgap power devices. These evaluated. These methods were tested on scaled-down versions advancements not only improve the reliability and performance of the target platform, validating the concept and demonstrating of power electronics systems but also pave the way for robust significant potential for online condition monitoring. This approach, predictive maintenance strategies, ensuring long-term sustainability informed by Failure Modes, Mechanisms, and Effects Analysis and operational efficiency in a wide range of applications. (FMMEA), sets the stage for enhanced reliability through informed Tangible results are amongst others maintenance strategies. newly developed hybrid DD-PoF model,

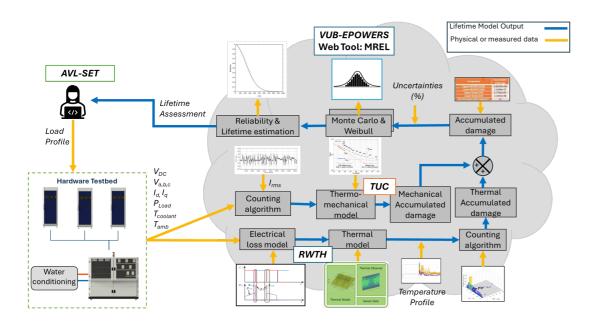

## Lifetime Testing

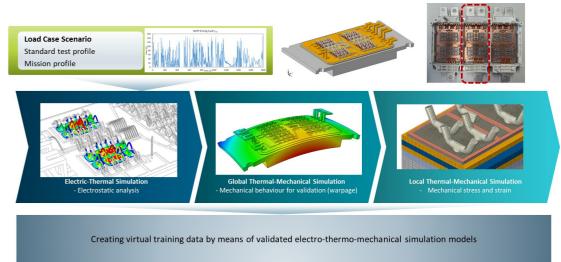

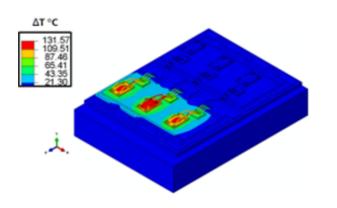

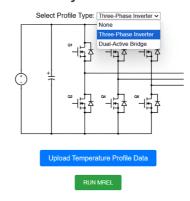

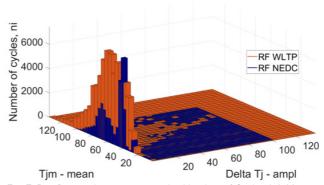

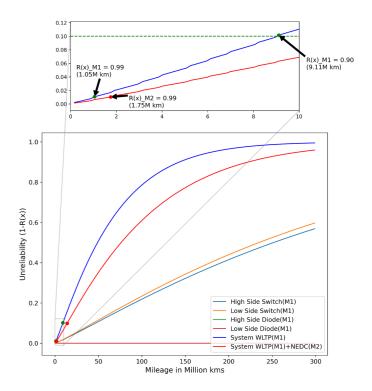

Within HiEFFICIENT, a novel power electronics lifetime testing setup has been developed, confirming the feasibility to assess series failure rates of power electronic components based on mission profile-oriented test data. A streamlined mission-profileoriented reliability assessment tool was developed that integrates mission profile-oriented measurements with data received from multi-physics models (i.e., electro-thermal and thermo-mechanical), significantly advancing lifetime prediction and failure risk assessment

Further, the project also placed a strong emphasis on lifetime testing and analysis of power modules, using novel integration methodologies for bare die embedding in a PCB. Thereby, outstanding durability values have been achieved, which are as follows. Various designs of embedded GaN power modules were tested using different GaN dies, specifically 80 V off-the-shelf and imec's 650 V SoC GaN bare dies. The 80 V dies achieved 290,000

- surrogate models for electro-thermal-mechanical fatigue for real-time assessment (Fig. 2) as well as according compact models ready for microcontroller implementation,

- PHM circuit to monitor ripple junction temperature (R<sub>1</sub>, ) to stay within limits,

- Mission-profile oriented reliability assessment tool for optimized design for reliability,

- Active thermal control concepts to minimize thermal cycling,

- Non-invasive junction temperature measurement with high bandwidth

- Mission profile oriented lifetime test system, and

- Highly reliable packaging concepts exceeding 500,000 power cycles under harsh conditions.

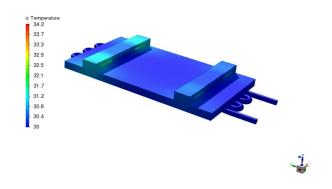

# **ADVANCED COOLING CONCEPTS FOR HIGHLY INTEGRATED POWER ELECTRONICS**

# INTRODUCTION

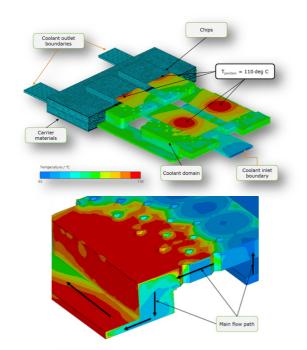

Latest wide-bandgap-based power electronic solutions can efficiently manage large amounts of power. Depending on the application, this can result in very compact designs that require effective heat dissipation. One of the primary challenges for the future miniaturization of electronics is its thermal management. With an increasing number of transistors per square centimeter, the generated heat fluxes will also rise. Forced air convection cooling has reached its limit and no longer satisfies the required thermal loads. Therefore, more sophisticated forced convection liquid and flow boiling cooling are being explored to meet thermal demands in the near future.

In this project, a highly efficient GaN-based amplifier was developed, featuring 48 GaN switches within an area of just 3.4 by 8 cm, releasing up to 1 kW of heat during full operation. This stretches conventional liquid cooling solutions to their limits, necessitating new approaches. Flow boiling in microchannels is a technology capable of absorbing high heat loads with a low flow rate and a compact design. A common issue in microfluidic flow boiling devices is the occurrence of boiling instabilities, which lead to reduced heat transfer and high-pressure fluctuations.

# PROGRESS BEYOND STATE OF THE ART

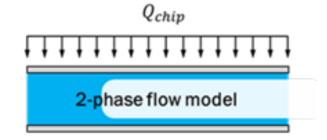

During the project, TNO focused to mitigate the named challenges and developed an advanced microfluidic flow boiling method. Within this project experiments, cooling capacities are achieved in the order of ~250 W/cm<sup>2</sup>, which is twice the current state-of-the-art achieved heatflux mentioned in literature. The stable pressure drop over the microfluidic cooler is below 100 mbar, as opposed to the reported several bars to pump the high flow rates through the microfluidic channels operated in literature. Finally, by choosing the appropriate cooling fluid the chip interface temperature is below 90°C, which ensures a junction temperature below 120°C at full operation power. This novel method does not require a complex hierarchical supply and outflow channel, typically seen in literature. To design this high-performance microchannel flow boiling cooling device, proper flow boiling models for microchannels are essential. Within the power electronics system the heat of the chip is first spread by the interposer in which the microfluidic flow boiling method is embedded. This reduces the local heat flux before it is absorbed by the cooling fluid. Existing state-of-the-art models do not take into account the heat spreading (Fig. 1) to predict the temperature of the chip.

Fig. 1 Schematics of flow a boiling model with fixed uniform heat flux cooled by a two-phase flow

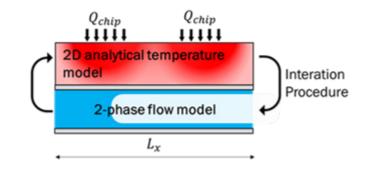

Fig. 2 Schematics of a flow boiling model with a coupled model for heat spreading and flow boiling.

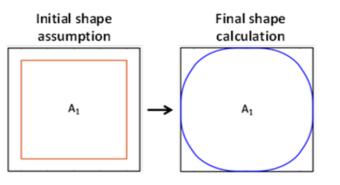

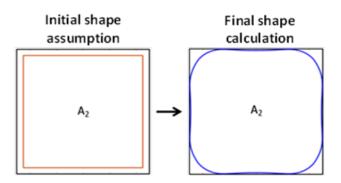

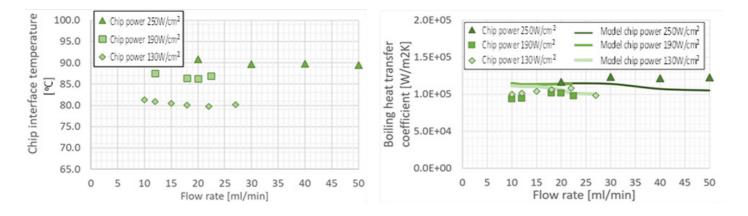

section is dependent on the amount of energy inserted in the fluid. The void fraction, however, strongly depends on the shape of the liquid film. An accurate prediction of the film thickness is essential for an accurate heat transfer coefficient prediction. In microchannels the shape of the liquid film is significantly affected by the surface tension. Based on equilibrium models found in literature, TNO developed a numerical method to calculate the equilibrium state of a liquid interface in a rectangular channel. The TNO model is extended with an empirical evaporation resistance and including this numerical method for the film thickness calculation. The effect of this inclusion on the liquid film shape can be seen in Fig 3.

The heat flux is assumed to be constant over the length of the channel. This constant heat flux assumption is inaccurate as the heat flux is a function of both the temperature of the heat spreader and the local boiling state of the fluid. To take the 2D heat spreading into account, a novel model is developed, coupling a 2D temperature model to a micro channel flow boiling model (Fig. 2). This coupled model is used as a design tool to optimize the dimensions of the cooling device. Hot spots or high peak temperatures are prevented. The TNO model calculates the flow boiling heat transfer coefficient using the thickness of the liquid film. The vapor mass fraction in a

Fig. 3 Surface tension effect on film shape for different void fractions, TNO microfluidic flow boiling model results. Left: void fraction 0.8. Right: void fraction 0.9

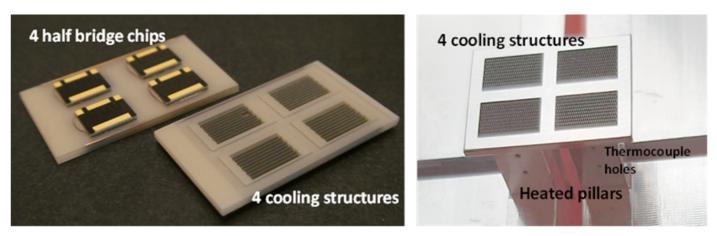

The improved modelling led to a microfluidic flow boiling design bottom of the microfluidic flow boiling structure. By means of the embedded in the interposer of the power electronics chips, see two thermocouple holes above each other, the vertical temperatu-Fig. 4 left. To validate the models and prove the calculated heated re gradient is measured in each pillar. This vertical gradient is used flux, an aluminum mockup setup is designed using heated pillars to estimate the wall temperature by linear extrapolation and assuwith the size of the chips, see Fig. 4 right. Therefore, this setup allming one dimensional conduction in the pillar. The heating power owed a better-defined thermal boundary condition. The aluminum supplied to the microfluidic flow boiling structure is derived as well pillar allows lateral heat conduction with a relatively small temperafrom the vertical temperature gradient. ture gradient, thus approaching the uniform wall temperature at the

Fig. 4 Left: top side with half-bridge chips, and bottom side with TNO microfluidic flow boiling cooler structure. Right: Aluminum mockup setup with the pillars to mimic the chip heat load and the thermocouple holes to estimate the heat flux and wall temperature

The temperature at the virtual chip interface and the microfluidic flow boiling heat transfer coefficient are determined for various chip powers. Fig. 5 (left), shows the chip interface temperature. Even for the highest power it remains slightly below 90°C. Using a typical internal chip resistance of about 0.8 K/W the junction temperature remains below 120°C at a chip dissipation of 40 W. Furthermore, the temperature is little dependent on the flow rate for one chip.

The heat transfer coefficient graph (right graph of Fig. 5) shows the model results with inclusion of the surface tension. A nice correspondence with the experiments is found. Both the near independence on the flow rate as well as the slight increase on increasing heat flux is captured by the model.

Fig. 5 Microfluidic flow boiling results: experiments (markers) and model (lines). Left: (virtual) chip interface temperature for three individual chip powers. Right: estimated microfluidic flow boiling heat transfer coefficient

# COMPACT AND HIGHLY **EFFICIENT ELECTRICAL** DRIVETRAINS

# INTRODUCTION

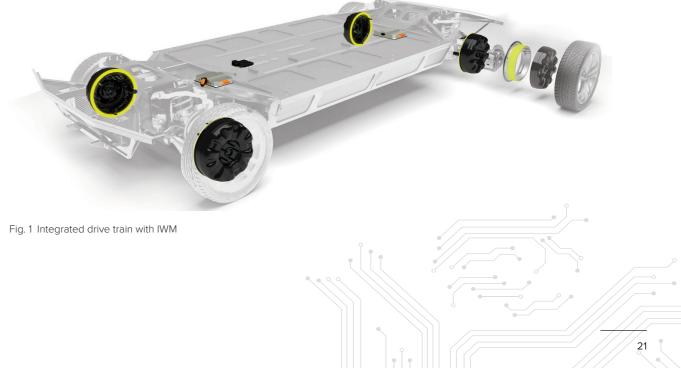

In the pursuit of greater energy efficiency, optimizing electric powertrains has become a central focus, as their design directly affects the performance, efficiency, and competitiveness of electric vehicles (EVs). A key aspect of this optimization is the integration of critical components, such as traction inverters, DC/DC converters, and onboard chargers (OBCs), which play a significant role in energy management and overall vehicle reliability. One of the most promising advancements in electric powertrain design is the development of highly integrated solutions. By optimizing system-level efficiency and reducing the volume of components, manufacturers can enhance vehicle performance while minimizing environmental impact. This integrated approach not only improves the powertrain's performance but also simplifies the vehicle architecture, creating a more userfriendly and efficient product. In parallel, the adoption of modular architectures further contributes to scalability and system reliability. This approach enables manufacturers to accommodate diverse vehicle platforms while ensuring that future technological advancements can be seamlessly integrated.

PROGRESS BEYOND STATE OF THE ART Silicon Carbide (SiC) and Gallium Nitride (GaN), HiEFFICIENT The HiEFFICIENT project is making significant progress achieves higher efficiency and power densities (3.6 kW to beyond the state of the art in electric vehicle (EV) powertrain 22 kW) than current market standards, while incorporating technology. A key area of innovation is the integration of Vehicle-to-Grid (V2G) functionality to enhance grid compatibility. bidirectional On-Board Chargers (OBCs) and DC/DC converters. A major leap forward in the project is its use of in-wheel motor By leveraging advanced semiconductor technologies like (IWM) technology. While IWMs are recognized for their potential in

# TANGIBLE RESULTS

The cooling performance of the microfluidic cooler containing the TNO microfluidic flow boiling method is measured by quantifying the chip interface temperature and the microfluidic flow boiling heat transfer coefficient. For the maximum investigated chip heat flux of 250 W/cm<sup>2</sup> the chip interface temperature remained below 90°C , which implies a junction temperature below 120°C. The low pressure drops (less than 100 mbar) over the microfluidic cooler are invoked by the low required liquid flow rates (far below 1 l/min for 1 kW heat removal). This leads to low pumping powers for the

### overall system.

The improved microfluidic flow boiling model captures the measured trends such as the increase of heat transfer coefficient on increasing the input heat flux and its relative independence on mass flow rate. The improved microfluidic modelling can be applied to design innovative cooler geometries for future cooling solutions, such as battery cooling and the integrated cooling of the housing of the electro-engine itself

torque vectoring and eliminating mechanical links such as driveshafts. This approach improves vehicle agility, handling, and drivability by enabling instantaneous control of torque distribution, especially during cornering, acceleration, and braking. The assistance systems (ADAS) and future autonomous vehicles. project's use of Elaphe IWMs further refines vehicle dynamics, marking a notable advancement in torque control systems. Another key innovation is the dual inverter platform, which supports IWM systems by integrating two independent threephase inverters in a single housing. This not only improves safety and reduces latency in torque vectoring but also lowers system complexity and costs, representing a practical solution for scalable EV architectures. The dual inverter setup ensures redundancy in case of motor failure, enabling more precise control and system resilience compared to conventional setups. HiEFFICIENT also pushes the boundaries in control response

EVs, HiEFFICIENT advances this by integrating highly responsive speed and bandwidth, addressing a critical limitation in traditional EV powertrains. By using direct-drive motors, the project achieves response rates far faster than the conventional 10 Hz limit, crucial for advanced driver-In summary, HiEFFICIENT advances the state of the art by improving powertrain integration, control precision, and efficiency. Its innovative use of IWMs, dual inverters, and advanced semiconductors sets new benchmarks for the next generation of high-performance, agile, and energy-efficient electric vehicles.

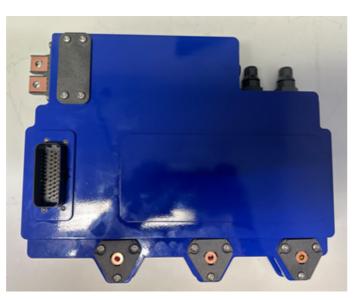

Within the HiEFFICIENT project a most compact powertrain has

been demonstrated. The smart multidrive unit developed in UC2a

can drive up to two motors for a total output power in the range of 500 kW occupying a volume of just 7.5 liters, including power connections and EMC filters. The unit provides a power density close to 70 kW/l (starting from 50 kW/l developed in HiPERFORM, but

having no EMC filter at this point in time!) which is an outstanding

value in the 400 V battery voltage range.

11 1 1 1 1 1

- 100 V SoC on GaN-on-SOI substrates

- 100 V SiP half-bridge

# KEY RESULT 5 - COMPACT AND HIGHLY EFFICIENT ELECTRICAL DRI-

- Multidrive inverter with 70 kW/I power density

- VETRAINS OBC with 7 kw/l power density

Fig. 2 Multidrive inverter

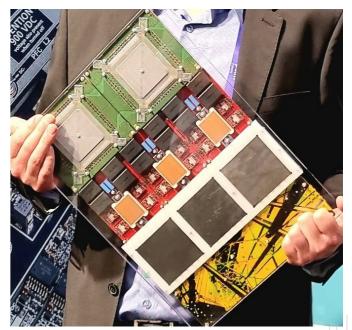

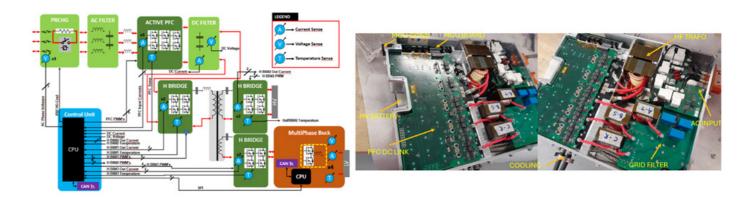

As another example, the integrated OBC+DC/DC converter developed in UC5c advances component integration by incorporating a bidirectional 3 kW DC/DC converter into a 22 kW OBC architecture. The resulting unit occupies approximately 13.7 liters, representing a volume reduction of over 15% compared to conventional standalone components. The efficiency between AC and HV DC reaches around 94-95%, while for the low-voltage DC section, we anticipate an efficiency above 92%.

Fig. 3 Integrated OBC + DC/DC converter

TANGIBLE RESULTS

# HIGHLIGHTS **KEY RESULTS**

# KEY RESULT 1 - FIRST GAN SIP AND SOC DEVICES OUT OF EUROPE

650 V SoC on GaN-on-poly-AIN substrates

# **KEY RESULT 2 - INTEGRATION METHODOLOGIES AND CONCEPTS** FOR HIGH POWER AUTOMOTIVE POWER ELECTRONICS

- 1200 V SiC half-bridge embedded in PCB

- 650 V GaN SoC on polyAIN embedded in PCB

- Sinterlamination with Cu-paste

- Highly reliable packaging concepts exceeding 500,000 power cycles under harsh conditions

# **KEY RESULT 3 - MAKE RELIABILITY AND PHM FUNCTIONS VISIBLE** AT THE TOP SYSTEM LEVEL AND TO THE END USER

- Hybrid DD-PoF model

- · Mission-profile-oriented reliability assessment tool for optimized design for reliability

- Active thermal control concepts to minimize thermal cycling

- Non-invasive junction temperature measurement with high bandwidth

- Mission profile oriented lifetime test system

# **KEY RESULT 4 - ADVANCED COOLING CONCEPTS FOR HIGHLY IN-TEGRATED POWER ELECTRONICS**

Microfluidic flow boiling capable of 250 W/cm<sup>2</sup> heat flux

Integrated OBC+DC/DC converter with 1.6 kW/I power density

# **ELECTRIFICATION TEST SYSTEMS** USING MODULAR CONCEPTS AND EMBEDDED POWER ELECTRONICS

Use case 1 focused on the development of test systems for validating the key electric and electronic components in electrified vehicles (EVs). Thereby three different focus topics have been followed, covering flexible converters with reduced size and new power levels, Prognostic Health Management (PHM) for power electronics in electrification testbeds and testing equipment for automotive power electronics lifetime testing.

In order to facilitate the shift towards electric mobility on a large scale, it is necessary to build massive test infrastructure for R&D, validation and quality assurance during production of all in-vehicle components as well as charging equipment. To keep the environmental impact low, this infrastructure must be built with a small ecological footprint and operated with low energy consumption. Designing compact, efficient and high dynamic power converters for test systems is a key element for achieving this goal.

When looking at the development of electrified vehicles in more detail, there is a need for cost efficient but high-fidelity testing solutions that replicates later customer usage as close as possible. Additionally, as the market evolves, testing requirements are getting broader and more complex. Hence, there is a strong need for flexible testing equipment, which can fulfil the needs of both component and vehicle manufactures. Particularly, Power-Hardware-in-the-Loop systems (P-HIL) are highly valued for the automated performance and lifetime testing of electric mobility components, like batteries, or any types of converters. Within

-

the P-HIL concept, the environment of the devices under test is emulated by power electronic converters. These converters have high signal quality requirements, which can only be achieved by using high frequency switching, digitally controlled amplifiers. The high switching frequency combined with optimized topologies and filters yields smooth signals up to a high bandwidth, prerequisite for accurately emulating component details, e.g., stray inductances of electric motors. Having said this, electrification test systems are therefore a challenging but ideal application field for wide-bandgap (WBG) semiconductors. Indeed, WBG devices are a necessity to achieve very high-fidelity emulating testing systems.

Along with the requirements for exceptional performance comes the need for a reliable and predictable operation of these solutions to minimize operational costs. Consequently, advanced power electronics control strategies and operation data analytics are important for a continuous and optimized operation.

To deliver the next generation of such test systems, following topics were in focus:

UC1a Flexible converters with reduced size and new power levels

- 1200 V SiC based power converter

- 650 V GaN based digital amplifier

- High performance control platform

UC1b Prognostic Health Management for power electronics in electrification testbeds

- 2 different approaches for Condition Monitoring and optimized operation

- Data analytics of operational data for failure prognosis

UC1c Testing equipment for automotive power electronics lifetime testing

# **FLEXIBLE CONVERTERS WITH REDUCED SIZE AND NEW POWER** LEVELS

Until today, so-called power stacks are used to build power Individual designs often lack the certainty of production quality and converters for such applications. These power stacks are an long field experience. assembly of discrete components: power semiconductor packages The other approach is to use ready-made power modules mounted on cooling plates, DC-link & snubber capacitors, highcontaining multiple transistors forming one or more half-bridges. current busbars, gate drive circuits and mounting frames. These power modules already combine electrical insulation with Typically, one stack is used for one application, which is designed for optimized thermal conductivity. However, the composition of such a given voltage and power level with a fixed number of phase legs modules is complex with several layers of materials with very and a target switching frequency. Any change of these parameters different physical properties, bonded high-current conductors, requires a time-consuming re-design and re-qualification of the substrate and filling materials. Such modules are difficult to entire stack, which limits the freedom in designing the test systems. manufacture with many production steps and thus expensive. The selection of predesigned modules limits the design freedom for One of the major challenges in power stack design is the ambivalence of the interface between power semiconductors new power converters

and the cooling plate: it shall provide as low thermal resistance as Alongside the course of this project, also the state-of-the-art progressed further with new technologies appearing on the possible on one hand, but it must also provide electrical insulation for reliable and safe operation. Most commonly, two different market, such as top side cooled discrete packages for low power applications or double-sided cooling modules for automotive approaches are used to bridge this gap. One is the design of converters with discrete power transistors in various forms of traction converters packages that provide relatively low thermal resistance but no Consequently, one area of development within UC1 have been power converters (DC/DC and DC/AC) and control platforms, electrical insulation. It is the converter designer's responsibility which are, e.g., used for battery pack and module testing, battery to ensure electrical insulation by using appropriate interface material between power transistor package and the heatsink or emulation equipment and for powering e-machines. Thereby cooling plate. The choice of interface material defines the tradea focus was on a scalable composition of electrification testing off between cooling and insulation. Although it provides design equipment catering different applications and testing requirements freedom, it is also prone to sub-optimal design and design errors. from a minimum number of base modules and consequently

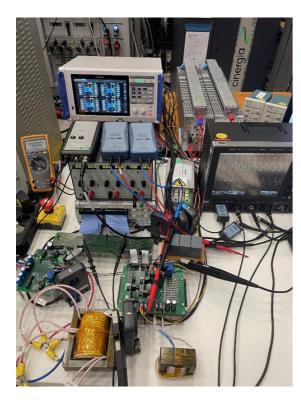

> This UC was conducted in a collaboration of six partners: AVL, AT&S, FHG, FHJ, IFAG, TNO

The contributions of each partner are described as follows:

AVL (UC LEAD): system specifications and design (PE, PHM), thermal simulations, micro-fluidic cooling circuit, control and P-HIL platforms

AT&S: embedded 1200 V SiC half-bridge power modules

FHG: support in chip metallization for chips embedding

FHJ: design and development of 1200 V SiC and 650 V GaN power converters

IFAG: providing 1200 V SiC dies

TNO: micro fluidic two-phase cooler for 650 V GaN power converter

.

following aspects were of main interest:

- Flexibility via modularity of testing equipment, to support different voltage and current ranges

- Creating compact, reduced size systems via high integration, e.g., embedding of power electronics with optimized cooling concepts.

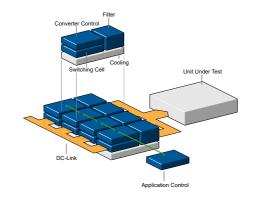

This concept of modularity is illustrated in Fig. 1. By designing different filters, the converters can be adapted to different testing needs. By parallel connection, the power can be scaled. And by changing the application control firmware, the test system can be switched between testing and emulating various types of units under test (UUTs), e.g. batteries. To achieve the set goals three main topics have been addressed in this sub use case:

Fig. 1 Modular composition of power converters for test systems

- 1200 V SiC based switching cell for different power converter applications, with a focus on PCB-embedding of power semiconductors for application voltages up to 1000 V DC

- 650 V GaN based digital amplifier making use of an advanced cooling system

- High performance control platform to combine numerous power stacks to achieve different power and voltage levels as well as supporting latest Power-Hardware-in-the-Loop (P-HIL) application requirements

## RESULTS

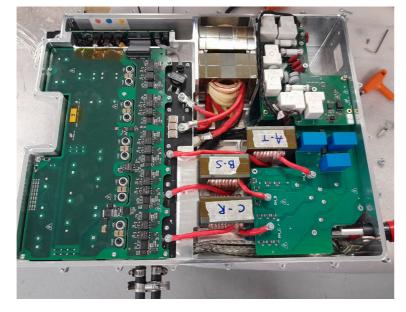

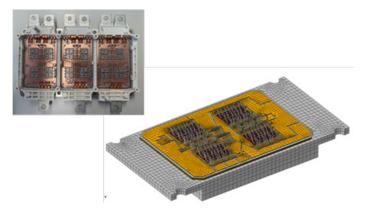

The initial subject covered in UC1a was the examination of the benefits of integrating chips directly into the PCB as opposed to traditional SMD-based approaches. The goal was to demonstrate advantages in power density and reliability. Therefore, project partners focused on two different implementations of a SiC switching cell for AVL's electrification testing solutions, guiding future application specs in a most compact format. FHJ thereby developed the reference design, using a discrete approach with 1200 V SiC-Mosfets in TO-247 casing. In parallel, AT&S created a half-bridge switching cell module, whereby 1200 V SiC Mosfets were embedded in the PCB. Each switching cell variant contains six half-bridges, applicable for, e.g., grid-tie-inverters, resonantconverters with galvanic isolation, DC/DC step-down converters or DC/AC inverters, but having the same form factor and hence being easily replaceable for comparison (Fig. 2). These two switching cell variants were chosen to study differences in loop inductance, thermal behaviour, and mechanical design. The developed prototypes achieved a 47% volume reduction in relation to today's baseline solution, achieving a power density of 6.4 kW/l. A certain aspect to achieve compact solutions and a reliable operation, is the thermal management. Therefore, a very efficient operation at high switching frequencies, i.e., 140 kHz, is key. Due to the potentials of

power electronics embedding, the loop inductance compared to the reference design could be halved. Furthermore, detailed investigations have been conducted to achieve the best possible thermal conductivity for most efficient cooling.

A matching grid-tie inverter filter was designed to build the first application converter with this SiC stack, which is shown in Fig. 3. Due to the embedding of dies in the PCB, the reliability of such power modules can be improved compared to other packages using wire bonds. Therefore, power cycling tests of the TO-247

Fig. 2 Reference design and embedded and assembled SiC stack

Fig. 3 125 kW SiC grid-tie inverter

and embedded SiC were carried out to benchmark the new modules. An impressive increase in lifetime was observed for the embedded devices compared to the discrete ones under comparable load conditions (junction temperature amplitude of 140 K). The TO-247 reference samples lasted up to 9000 cycles. Device failure

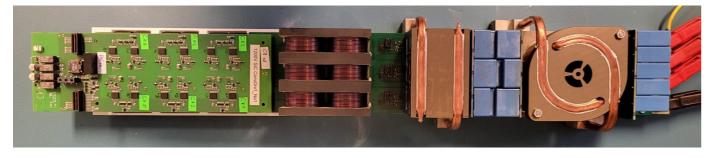

Fig. 4 90 kW GaN digital amplifier design for 2.5 MHz interleaved switching frequency

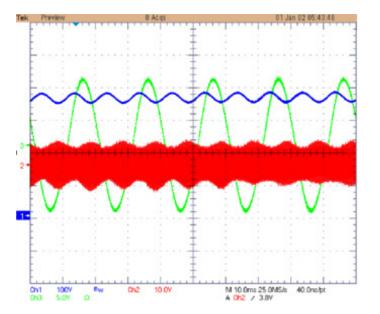

Secondly, a 650 V GaN based digital amplifier has been developd. Again, a part of the design was implemented with two different technologies with the goal to make a comparison in the same application use case. The very small GaN transistors pose a problem with very high heat dissipation per unit area. Hence, two different cooling concepts have been tailored to the GaN digital amplifier stack: a classical approach with a contour-milled aluminum cold

Fig. 5 Micro-fluidic cooler assembly (left) attached to the bottom side of the GaN amplifier (right)

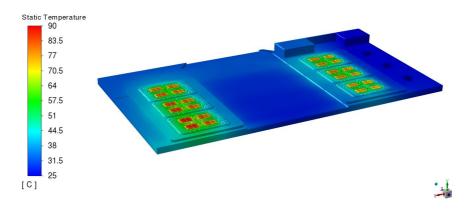

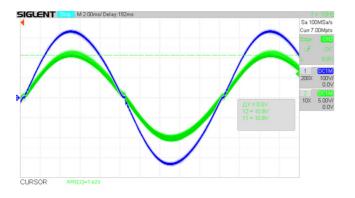

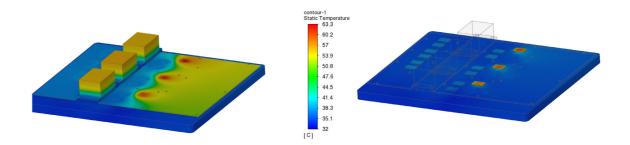

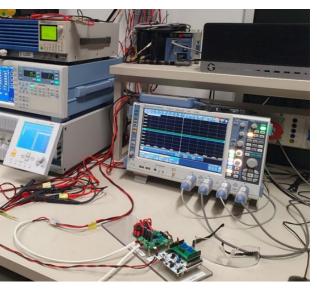

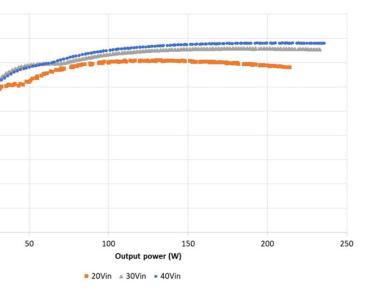

Prototypes of the basic switching cell could be tested successfully of a multiphase phase evaporation cooling is the proper approach up to 30 A per pair of coupled half-bridges at a DC-link input volto investigate such kind of problems. The simulation domain is ditage of 400 V. The full amplifier contains 6 such half-bridge pairs, splayed in Fig. 6 (top) showing one segment with four GaN chips resulting in a total output current of 180 A DC. Simulation studies on top of the multi-layer solid structure. In this illustrated examindicate that this amplifier will be able to achieve a voltage slew ple, the four chips provide a heat input of 4 x 20 W into the segrate of 300 V in less than 10 µs at the filtered output with a steady ment. A fluid mixture is entering the domain with a temperature of state ripple lower than 0.15 Vpp. This allows the emulation of DC 35 °C. The applied RPI (Rensselaer Polytechnic Institute) wall boiling and AC grids with a high fidelity and a bandwidth of 150 kHz as model is an advanced approach to deal with the nucleate boiling an example. The goal is to replicate not only the harmonics of the regime. The basic model assumes that the vapor phase is always grid frequency or the residual ripple of a DC bus but also parasitic at saturation conditions and only evaporation is modelled due to impedances of cable connections. Not only for this use case, but heated walls (defined as temperature or heat flux boundary condifor power electronics in general, 3D studies of liquid cooling are tions, or multi-material interfaces). A major target in this simulation essential because local flow characteristics on the coolant side is the average temperature at the interface between the chips and have a significant impact on cooling effectiveness and hot spots. the interposer material which is kept at approx. 83°C which is well Beside classical thermal response studies, such as conjugate heat within specified limits. transfer in structures and single-phase cooling approach in fluid Due to the wide range of different setups that can be generated with different combinations of approaches, sub-models, and boundomains, the focus of this work was more on the proper simulation of the cooling design for a liquid cooling system to picture the codary conditions specification, the improvement of the model stabioling performance in a more accurate way. A 3D-CFD simulation lity is able to consider many different aspects.

# USE CASES - UC1A

As a qualitative measure the distribution of the built-up of the vapor volume fraction of the coolant is also checked (Fig. 6 (bottom)). Together with other quantities, such as flow field parameters, it provides ideas to improve the flow path and thus also the heat transfer. The final design of the micro-fluidic cooling assembly could be tested in a dedicated test setup. With a power dissipation of 20 W per chip (total: 48 chips per amplifier) and an elevated inlet temperature of 60°C, a surprisingly low flow rate of less than 5 ml/min per chip is required to keep the junction temperature at a maximum of 110°C. This makes it possible to use a simple condenser to dissipate the waste heat to the ambient air without an additional chiller. Alongside the development of modular power building blocks, a cutting-edge control platform has been devised, enabling the flexible combination of multiple power stacks either in parallel or series to meet specific requirements for voltage and current in various applications. The research also prioritised the advancement of Power-Hardware-in-the-Loop (P-HIL) solutions, which are crucial for the automated testing of electric mobility components. Central to this P-HIL system is a versatile power stack paired with a control unit capable of functioning across different applications by adapting the control software and related components like filters and inductors. The power stacks developed in UC1a will be integrated into this setup, catering to diverse testing scenarios.

## IMPACT OF UC1A

The technology developed within this use case is a great step forward in manufacturability of high power density converters. It allows more parts to be integrated into PCBs, thus reducing the need for interconnections with cables and busbars. Although the complexity of the PCBs themselves certainly rises, the number of assembly steps for the converters can be reduced and the high degree of automation provides economies of scale to reduce cost, optimize material usage and greatly improve quality.

The resulting compact converter modules can be arranged in different applications. They can be scaled in power, current, and voltage. Combined with greatly increased robustness and lifetime, the

resulting test systems can be used for many years, even with high utilization. The long operation life also reduces the ecological impact of manufacturing.

The tight integration reduces parasitic loop inductance such that the full advantage of the SiC semiconductors can be utilized for high dynamic output control and higher efficiency. The consequent reduction of filter size also contributes to the reduction of raw material usage and converter size and thus the environmental impact.

Furthermore, UC1a was setup with dedicated interfaces between the individual functional layers, such that technologies can be exchanged within the layers and meaningful benchmarks can be executed in comparable settings. This allows for careful selection of technologies and variants on the way towards product development. It is possible to evaluate power traditional semiconductor packaging compa-

Fig. 6 Simulation domain (top) and vapour formation along the flow path (bottom)

red to PCB embedding, different cooling concepts, gate drive, and control circuitry - all independently of each other.

The applied simulation approach for the evaporation cooling provides the proper tools to start investigations in an early stage of the design because local flow characteristics on the coolant side have a significant impact on cooling and its performance. And problems which are detected early in advance can avoid expensive cycles of iteration during prototyping and manufacturing phase.

Furthermore, the application of these physical models includes most of the thermal management systems (e.g., general cooling phenomena in power electronics, water cooling jacket, battery cooling) in which evaporation phenomena are used to absorb heat and carry it out of the system.

# UC1a Achievements

rate

47% volume reduction

Ŵ

(a)

- GaN amplifier with 625 kHz switching

- frequency and 2.5 MHz ripple frequency 250 W/cm<sup>2</sup> heat transfer with reduced cooling system size: 90% reduction in size and flow

50 times longer lifetime of embedded 1200 V SiC half-bridge modules compared to conventional TO-247 packages

Single control platform for multiple converter control

UC1B

# **PROGNOSTIC HEALTH MANAGEMENT** FOR POWER ELECTRONICS IN **ELECTRIFICATION TESTBEDS**

The UC1b demonstrators assessed the feasibility of condition monitoring and Prognostic Health Management (PHM) to improve power electronics in electrification test fields through three solutions. The first approach used gate driver manipulation to maintain constant losses, and the second employed non-invasive temperature measurements to adapt system performance. The final data-driven method, developed with UC2a, analysed logged parameters to determine system health. All methods were tested on scaled-down versions of the potential target platform using identical components for straightforward proof of concept.

# RESULTS

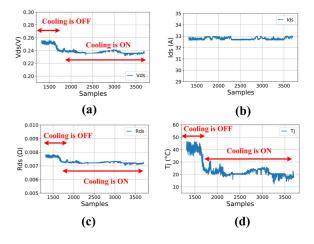

electrothermal condition monitoring system was designed for inverter systems. It uses the temperature sensor integrated into the power module to estimate the junction temperature. Moreover, an adaptive gate driver system was developed to manipulate gate voltage and control the junction temperature, effectively reducing thermal cycling. Laboratory tests showed that the Active Thermal Control (ATC) system reduced thermal cycles, potentially enhancing the lifespan of the power module.

Gate driver manipulation As a part of the project, a detailed power loss model has been developed to estimate conduction and switching losses of a multichip SiC power module, using manufacturer data and electrical parameters. In addition to that, a compact thermal model of the power module was also created. Based on the electrothermal model, an observer-based real-time

Fig. 1 Operation of the observer-based condition monitoring system

AVL, RWTH, SAL, VIF

The contributions of each partner are described as follows:

AVL (UC LEAD): system requirements and provision of test vehicle

RWTH: 3D and compact thermal modelling of the multi-chip power module; real-time condition monitoring and active thermal control systems

SAL: real time condition monitoring based on virtual junction temperature estimation

VIF: data-driven modelling on reliability and PHM

Fig. 2 Operation of the active thermal control system

# This UC was conducted in a collaboration of four partners:

# Non-invasive Thermal Control

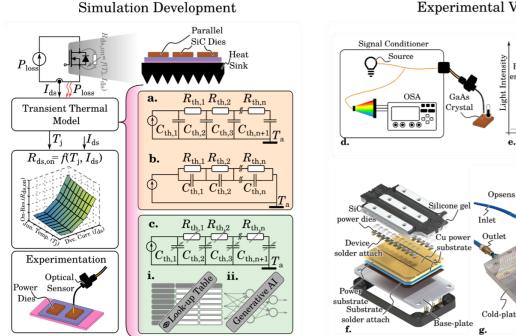

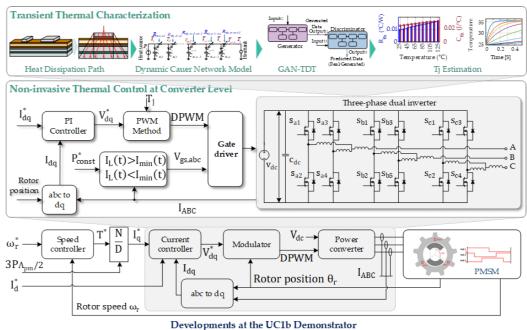

UC1b further includes the development and integration of a noninvasive thermal control system aimed at enhancing the lifespan of SiC MOSFETs. A key contribution is the development of a transient thermal model for real-time estimation of the junction temperatures (T.) within the power module. This model is trained using both synthetic and experimental thermal data to optimize thermal management. Integrated into the UC1b's inverter topology, the system uses real-time temperature data to dynamically adjust switching patterns, minimizing thermal load and optimizing the performance of the power electronics.

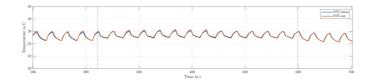

The non-invasive thermal control system involves transient thermal characterization of SiC MOSFETs in the UC1b demonstrator, validated through both simulation and experimental frameworks using the CAS480M12HM3 SiC power module as shown in Fig. 3. Simulations are conducted in MATLAB/Simulink and PLECS environments and compared with experimental data from Opsens GaAs fiber-optic sensors. The models include a generative adversarial network-based temperature-dependent thermal (GAN-

TDT) framework for measuring temperatures across multiple dies. The GAN-TDT model is trained by optimizing the generator (G) and discriminator (D) networks over 1000 epochs using the Adam optimizer. In the closed-loop simulation, the trapezoidal rule solver (ode23t) estimates T, iteratively, using power loss calculations to refine thermal parameters. Experimental validation, performed using fiber-optic sensors mounted on the power module cooled by a Q-ATS cold plate, measured T, at two dies to account for thermal cross-talk. Calibration against known temperatures ensured accuracy, with average estimation errors of 2.17% for the central die and 4.52% for the peripheral die, confirming the model's effectiveness. Further, the trained model's bandwidth was assessed by calculating the power spectral density, yielding an average bandwidth of 20.03 Hz, confirming its ability to capture dominant thermal response characteristics. For the UC demonstration, the model is deployed with the simulated converter topology operated with a torque profile and the average estimated temperatures for the power module operation are shown in Fig. 4.

Fig. 4 Dynamic response of MOSFET and diode junction temperatures under varying torque. Solid red line denotes MOSFET temperature, blue dashed line indicates diode temperature (°C, left y-axis), and green line shows torque profile (Nm, right y-axis)

The thermal control focuses on integrating the GAN-TDT model pulse width modulation (DPWM) to minimize converter power loss to provide real-time temperature estimates and assess control through the workflow shown in Fig. 5. strategies like field-oriented control (FOC) and discontinuous

Fig. 3 Process flow for transient thermal characterization. The workflow illustrates the use of (a) Cauer, (b) Foster, and (c) temperature-dependent Cauer models with (i) look-up tables and (ii) generative AI. On-state resistance is adjusted dynamically based on estimated junction temperature(T) from the RC thermal network and drain current. Estimated T, is validated using fiber-optic sensors. (d) Temperature change detected via GaAs-based fiber optic measurements using an Optical Spectrum Analyzer (OSA), and (e) temperature-wavelength relationship, where higher temperatures shift the band-gap spectral position. (f) Layer stack-up of CAS480M12HM3 power module, with seven layers modelled for transient thermal analysis. (g) Hardware setup with SiC power module, fiber-optic cables, and cold-plate, measuring T, at two paralleled dies (periphery and center) to capture thermal cross-talk

Band-gap

**Opsens Fiber-optic**

Wavelength  $(\lambda)$

Open

Probe-hold

Fig. 5 Integrated Thermal Control System for SiC MOSFETs in Dual Inverter Configuration with PMSM drive. The system utilizes a GAN-TDT model for accurate junction temperature estimation and employs discontinuous pulse width modulation to optimize switching events based on thermal feedback, minimizing power loss, and reducing thermal stress

The UC1b dual inverter system was modelled in Simulink, where block, provided real-time power loss estimates to guide DPWM FOC managed torque and speed of the PMSM, while DPWM adjustments for effective thermal management, identifying stress optimized switching based on estimated junction temperatures to points. reduce MOSFET thermal stress. The model operated under the Simulations demonstrated balanced phase currents and stable similar torque profile as shown in Fig. 4 with a 20 kHz switching torque control with minimal distortions. The rotor speed remained frequency. The GAN-TDT model, integrated as a custom MATLAB around 3000 rpm, showing the system's responsiveness to load

smoothly after minor overshoots, demonstrating effective control. Power loss comparison between FOC-SVPWM and the new thermal control system showed the latter limited power loss to under 150 W, significantly improving thermal management and

changes. D-axis and q-axis currents in FOC scenarios converged overall inverter efficiency. This in turn leads to decreased thermal stress in power devices suggesting a potential lifetime extension of approximately 1.5% as shown in Fig. 6, with further experimental validation required.

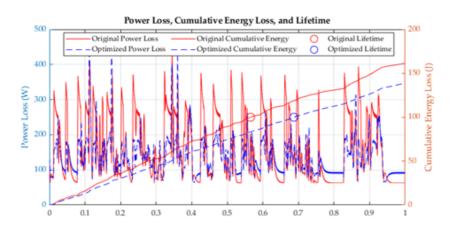

Fig. 6 Comparison of original controller and optimized thermal management systems showing power loss (W, left y-axis) and cumulative energy loss (J, right y-axis). Solid red lines indicate original power metrics, while dashed blue lines represent optimized results. Circular markers depict estimated device lifetime, highlighting a 1.5% extension achieved through reduced power loss and improved thermal efficiency

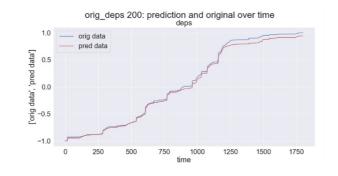

## DD methodologies for health/damage prediction

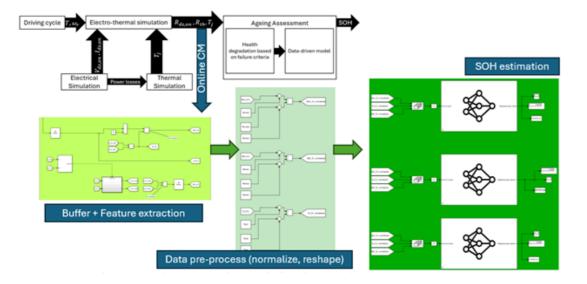

The Data-Driven (DD) methodology has been developed considering the most common failure mechanisms. The following methodology is explained in detail in UC2a. As a summary, one method for estimating the State of Health (SoH) involves utilization of data-driven models, which typically necessitate extensive datasets from accelerated aging tests or condition monitoring. Considering the limited availability of such data, a MATLAB

Simulink-based electro-thermal model was developed to generate data. The junction temperatures of the switches were evaluated using a Foster equivalent thermal network. This synthetic data enabled the development of Deep Neural Network (DNN) models using Convolutional Neural Networks (CNN) and Long Short-Term Memory (LSTM) NN in Python. The models can be used to estimate the SoH of SiC MOSFETs and are integrated into MATLAB Simulink for further analysis. The workflow is shown in Fig. 7.

Fig. 7 Workflow of the approach including online monitoring - results from electro-thermal simulations are used for the DD model; model is altered to predict the SOH in close to real time - buffer is created to store the data - feature extraction and data preprocessing occurs and then the signals are passed on to the models for DD estimation

For Data Driven (DD) approaches, data acquisition step is naturally followed by performing feature engineering. This process is used to generate new features by forming linear combinations of existing ones, resulting in a distinct feature set, with potentially higher correlation with the label set. The selected features are  $R_{ds on}$ ,  $R_{th}$ , and  $T_{t}$ .

In supervised learning, each feature must be linked to a corresponding label, necessitating the calculation of labels based on failure criteria. These output labels, which reflect the model's predictions, are crucial for training the neural network (NN). In this study, the label represents the State of Health (SoH) of the power modules, with values ranging from 0% to 100%. A SoH of 100% indicates optimal device performance, whereas a SoH of 0% signifies that the device has reached its end of life and requires maintenance or replacement. To ensure redundancy, three methods are employed for SoH calculation, like increase of R<sub>dean</sub>, R<sub>th</sub> and T<sub>u</sub>, compared to the value in the first thermal cycle. If certain thresholds are exceeded, the failure criteria are triggered for further action and respective maintenance.